DE0-Nano Cистема на кристалле. Часть 3

Создание системы на кристалле. Часть 3

Заключительная статья о создании прошивки для ПЛИС.

После того, как разработано ядро для работы с АЦП, можно приступить непосредственно к созданию SOPC.

Для этого необходимо добавить следующие компоненты:

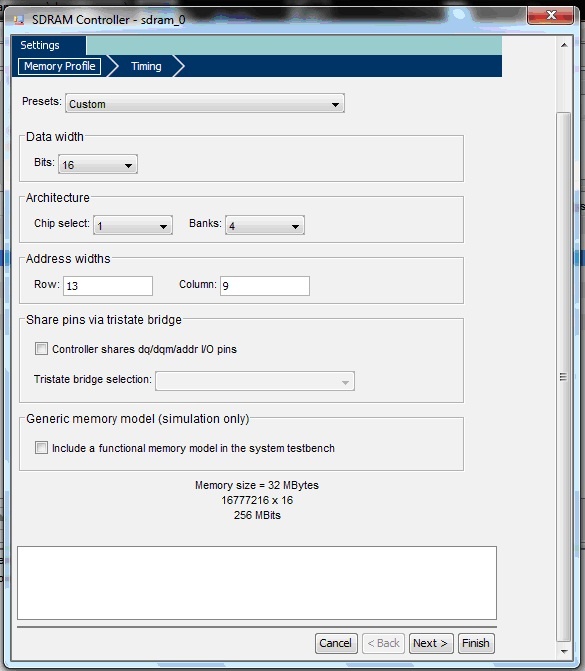

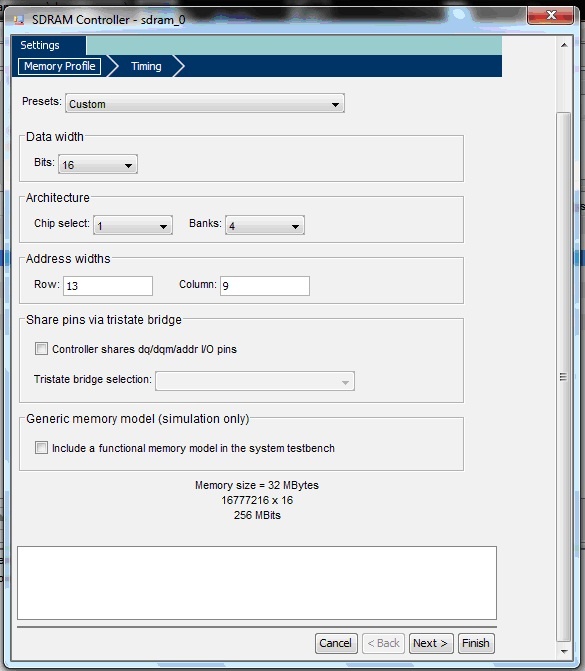

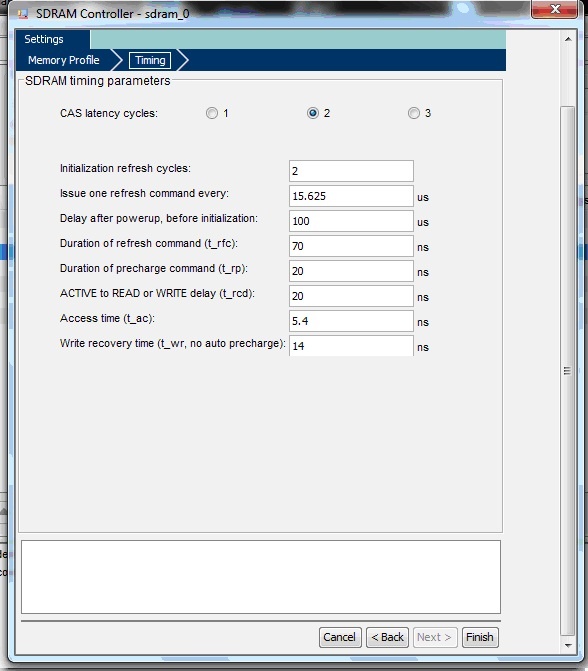

SDRAM Controller, контроллер памяти:

Все временные параметры памяти можно посмотреть в даташите на микросхему.

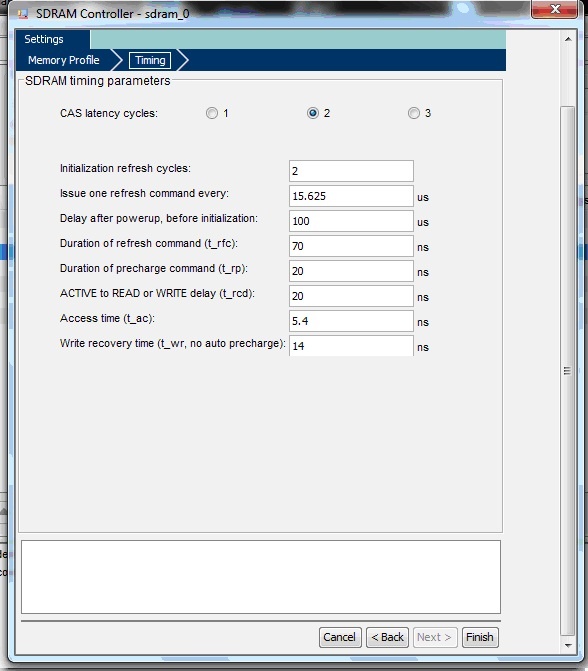

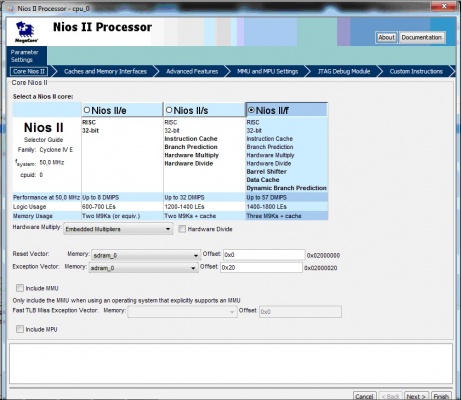

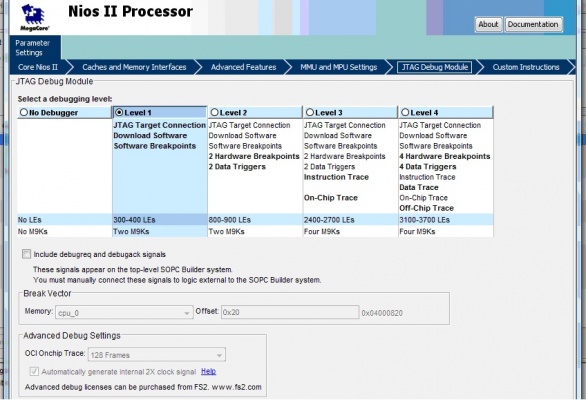

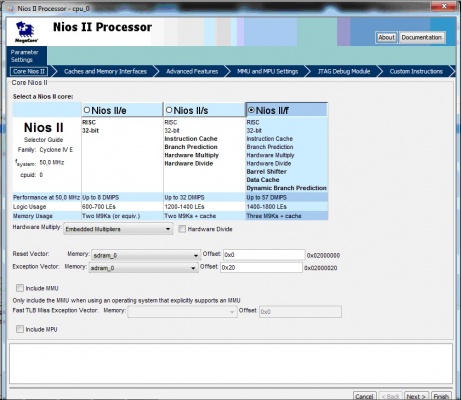

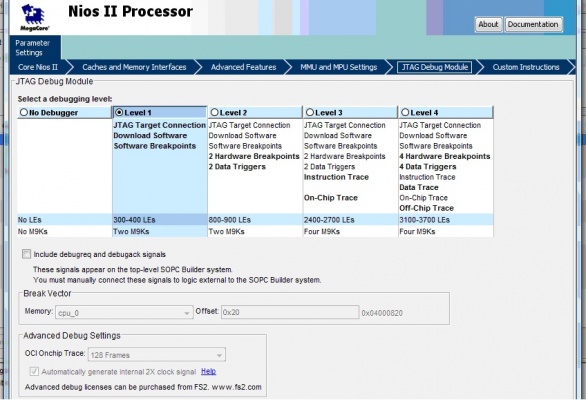

Процессор NIOS:

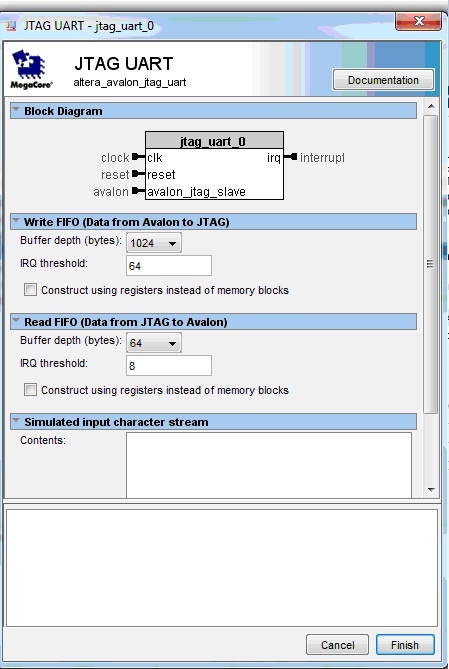

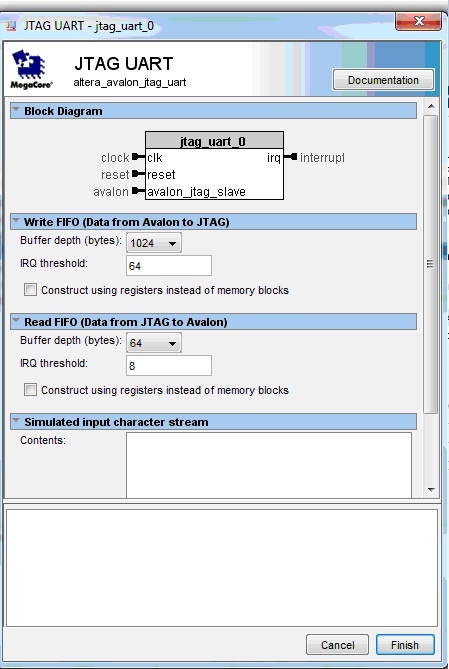

JTAG UART, используется для отладки, а также для передачи данных с АЦП на хост-компьютер:

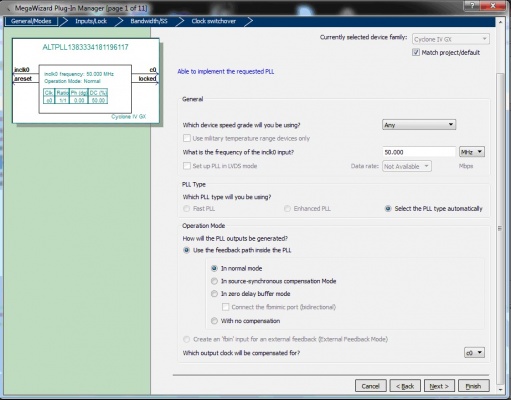

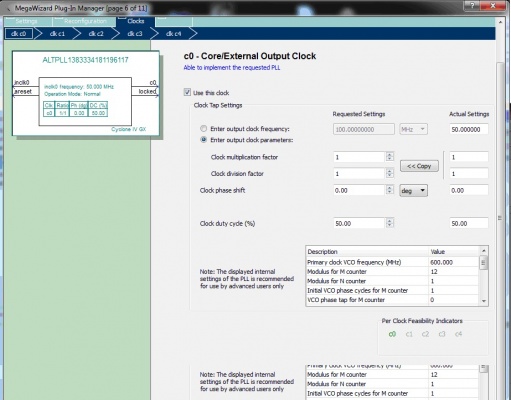

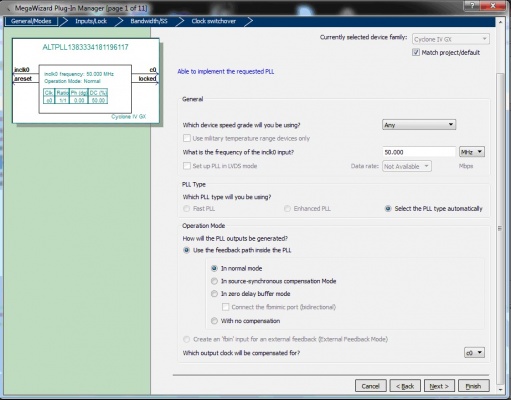

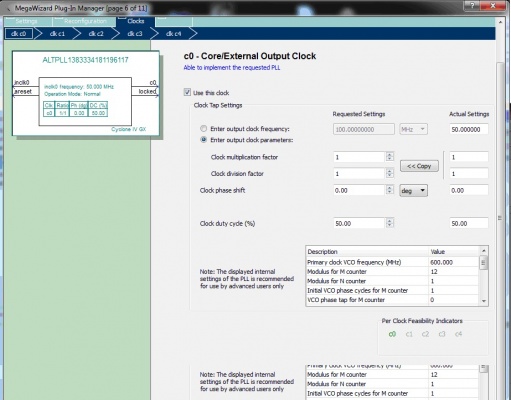

PLL для тактирования, в качестве входа используется расположенный на отладочной плате генератор 50Mhz. Выходной сигнал также выводится на внешний пин для тактирования микросхемы памяти.

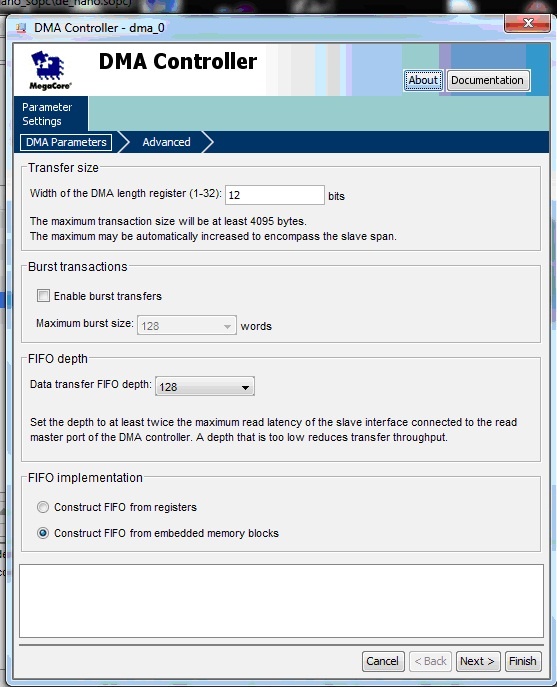

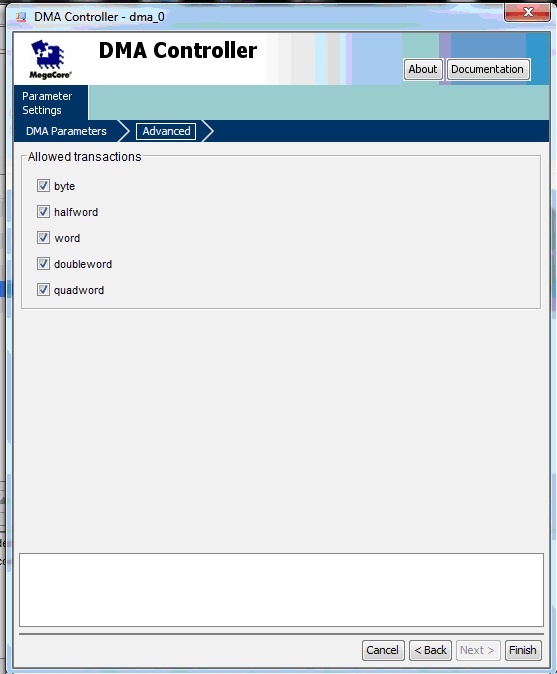

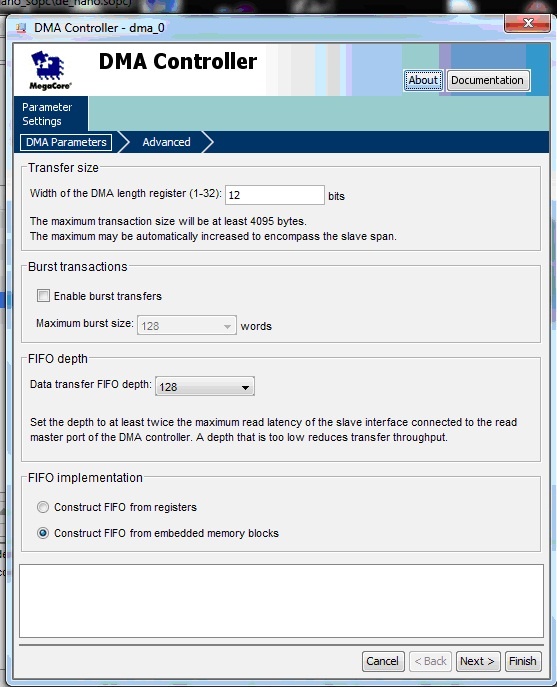

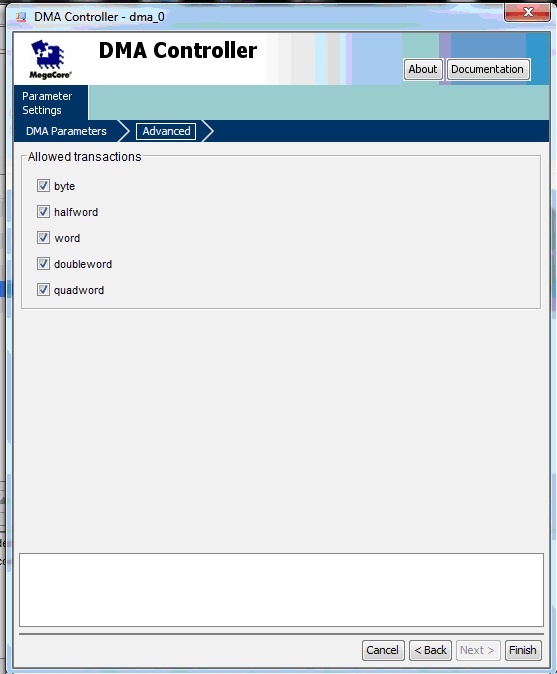

DMA controller, из параметров можно указать максимальную длинну одной транзакции DMA в словах, а также формат слова:

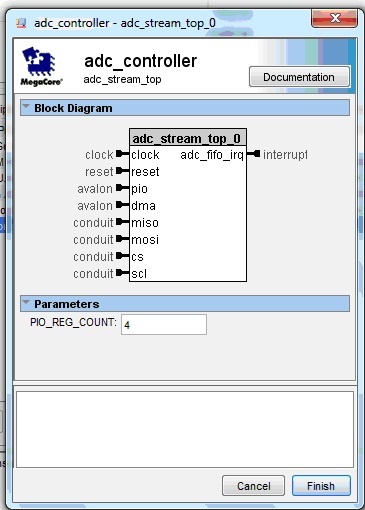

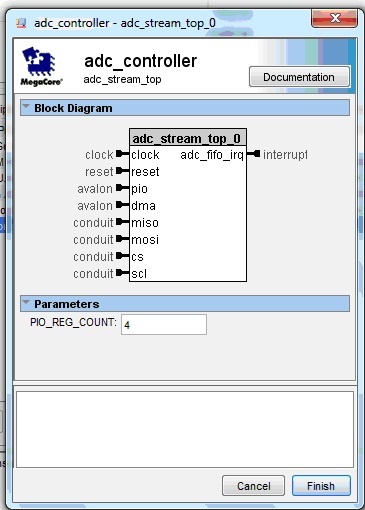

И собственно сам контроллер АЦП, здесь в качестве параметров можно настроить количество доступных регистров, в нашем случае достаточно четырех таких регистров:

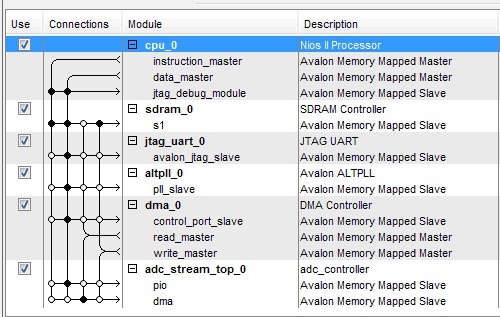

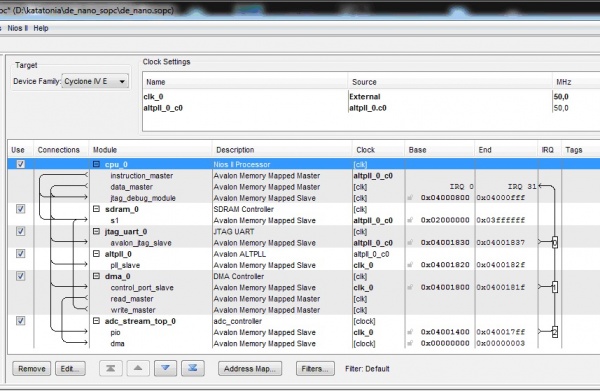

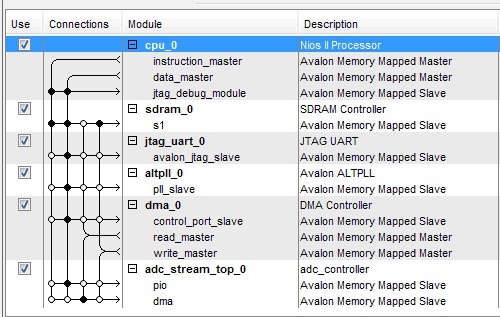

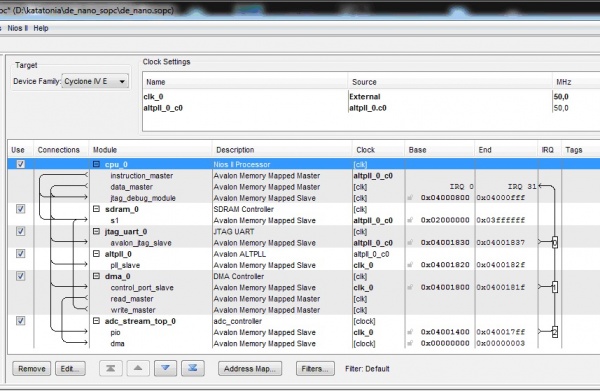

После того, как все компоненты добавлены, необходимо соединить их между собой:

Особое внимание при этом уделю DMA контроллеру, который имеет три интерфейса:

Control_port_slave – для чтения и записи регистров контроллера DMA из процессора

Read Master – Шина для чтения данных, подключается к интерфейсу dma компонента adc_stream_top_0.

Write Master –Шина для записи данных, подключается к контроллеру памяти

Шина PIO контроллера АЦП подключается к процессору к интерфейсу data_master, смысл этого в том, что регистры АЦП отображаются в общее адресное пространство процессора и обеспечивается возможность доступа к ним из программы.

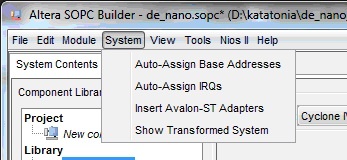

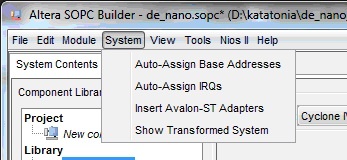

Базовые адреса для компонентов и номера прерываний назначаются пунктами меню System:

После всего проделанного должно получиться что-то вроде такого:

Описание системы на кристалле для Quartus сформируется после нажатия кнопки Generate. В папке с проектом помимо всех прочих файлов будет сгенерирован файл de_sopc_inst.vhd, содержащий описание сгенерированного блока для его вставки в top-модуль проекта.

Таким образом, top-модуль проекта будет выглядеть после вставки sopc:

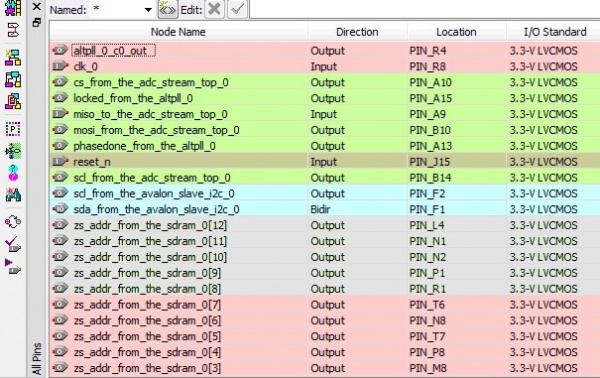

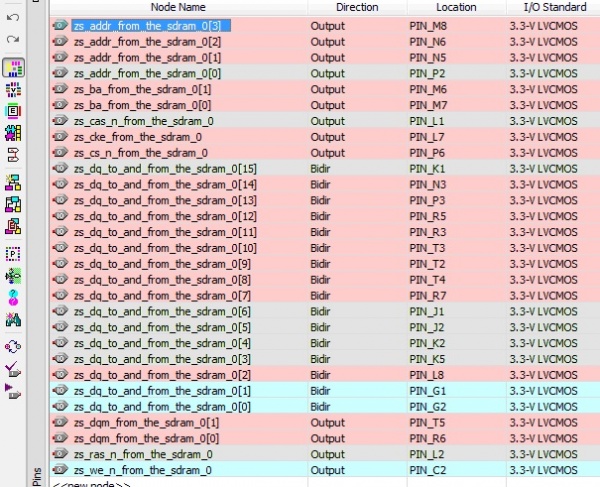

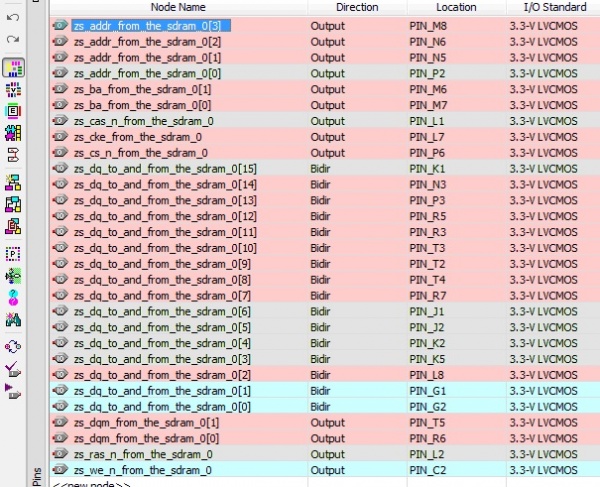

Большинство портов относится к SDRAM памяти, для которой помимо сигналов адреса, данных и т.д. выведен тактирующий сигнал от PLL. Все порты в заголовке выводятся на внешние контакты ПЛИС:

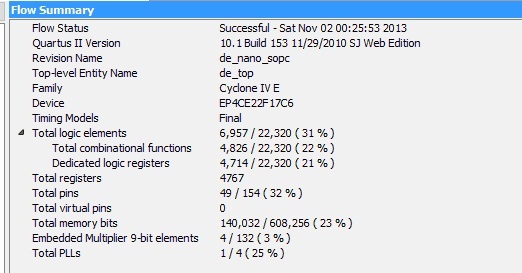

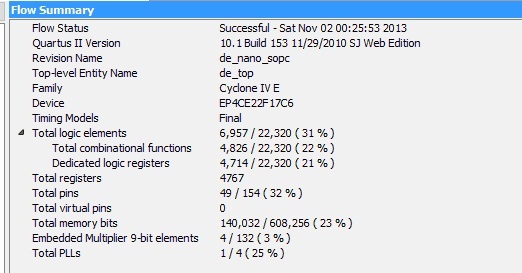

Разводку выводов по плате можно посмотреть в документации на DE0-nano. После компиляции имеем готовую прошивку. А также описание системы на кристалле в формате .sopcinfo. Это файл будет использоваться в дальнейшем при создании программно обеспечения в среде Nios II 10.1 Software Build Tools for Eclipse.

Заключительная статья о создании прошивки для ПЛИС.

После того, как разработано ядро для работы с АЦП, можно приступить непосредственно к созданию SOPC.

Для этого необходимо добавить следующие компоненты:

SDRAM Controller, контроллер памяти:

Все временные параметры памяти можно посмотреть в даташите на микросхему.

Процессор NIOS:

JTAG UART, используется для отладки, а также для передачи данных с АЦП на хост-компьютер:

PLL для тактирования, в качестве входа используется расположенный на отладочной плате генератор 50Mhz. Выходной сигнал также выводится на внешний пин для тактирования микросхемы памяти.

DMA controller, из параметров можно указать максимальную длинну одной транзакции DMA в словах, а также формат слова:

И собственно сам контроллер АЦП, здесь в качестве параметров можно настроить количество доступных регистров, в нашем случае достаточно четырех таких регистров:

После того, как все компоненты добавлены, необходимо соединить их между собой:

Особое внимание при этом уделю DMA контроллеру, который имеет три интерфейса:

Control_port_slave – для чтения и записи регистров контроллера DMA из процессора

Read Master – Шина для чтения данных, подключается к интерфейсу dma компонента adc_stream_top_0.

Write Master –Шина для записи данных, подключается к контроллеру памяти

Шина PIO контроллера АЦП подключается к процессору к интерфейсу data_master, смысл этого в том, что регистры АЦП отображаются в общее адресное пространство процессора и обеспечивается возможность доступа к ним из программы.

Базовые адреса для компонентов и номера прерываний назначаются пунктами меню System:

После всего проделанного должно получиться что-то вроде такого:

Описание системы на кристалле для Quartus сформируется после нажатия кнопки Generate. В папке с проектом помимо всех прочих файлов будет сгенерирован файл de_sopc_inst.vhd, содержащий описание сгенерированного блока для его вставки в top-модуль проекта.

Таким образом, top-модуль проекта будет выглядеть после вставки sopc:

library ieee;

library work;

use ieee.std_logic_1164.ALL;

use ieee.numeric_std.ALL;

entity de_top is

port

(

-- 1) global signals:

clk_0 : in std_logic;

reset_n : in std_logic;

altpll_0_c0_out: out std_logic;

locked_from_the_altpll_0: out std_logic;

phasedone_from_the_altpll_0: out std_logic;

-- the_sdram_0

zs_addr_from_the_sdram_0 : out std_logic_vector (12 downto 0);

zs_ba_from_the_sdram_0 : out std_logic_vector (1 downto 0);

zs_cas_n_from_the_sdram_0 : out std_logic;

zs_cke_from_the_sdram_0 : out std_logic;

zs_cs_n_from_the_sdram_0 : out std_logic;

zs_dq_to_and_from_the_sdram_0 : inout std_logic_vector (15 downto 0);

zs_dqm_from_the_sdram_0 : out std_logic_vector (1 downto 0);

zs_ras_n_from_the_sdram_0 : out std_logic;

zs_we_n_from_the_sdram_0 : out std_logic;

cs_from_the_adc_stream_top_0: out std_logic;

mosi_from_the_adc_stream_top_0: out std_logic;

miso_to_the_adc_stream_top_0: in std_logic;

scl_from_the_adc_stream_top_0: out std_logic

);

end de_top;

architecture arc of de_top is

begin

sopc_i: entity work.de_sopc

port map

(

altpll_0_c0_out => altpll_0_c0_out, --SDRAM Clock из PLL

locked_from_the_altpll_0 => locked_from_the_altpll_0,

phasedone_from_the_altpll_0 => phasedone_from_the_altpll_0,

zs_addr_from_the_sdram_0 => zs_addr_from_the_sdram_0, --SDRAM Address

zs_ba_from_the_sdram_0 => zs_ba_from_the_sdram_0, --SDRAM Bank

zs_cas_n_from_the_sdram_0 => zs_cas_n_from_the_sdram_0, --SDRAM CAS

zs_cke_from_the_sdram_0 => zs_cke_from_the_sdram_0,

zs_cs_n_from_the_sdram_0 => zs_cs_n_from_the_sdram_0, --SDRAM CHIP SELECT

zs_dq_to_and_from_the_sdram_0 => zs_dq_to_and_from_the_sdram_0, --SDRAM DATA

zs_dqm_from_the_sdram_0 => zs_dqm_from_the_sdram_0, --SDRAM DQS

zs_ras_n_from_the_sdram_0 => zs_ras_n_from_the_sdram_0, --SDRAM RAS

zs_we_n_from_the_sdram_0 => zs_we_n_from_the_sdram_0, --SDRAM Write Enable

clk_0 => clk_0, --входной тактовый сигнал

reset_n => reset_n, --сброс

--SPI

cs_from_the_adc_stream_top_0 => cs_from_the_adc_stream_top_0,

mosi_from_the_adc_stream_top_0 => mosi_from_the_adc_stream_top_0,

scl_from_the_adc_stream_top_0 => scl_from_the_adc_stream_top_0,

miso_to_the_adc_stream_top_0 => miso_to_the_adc_stream_top_0

);

end arc;

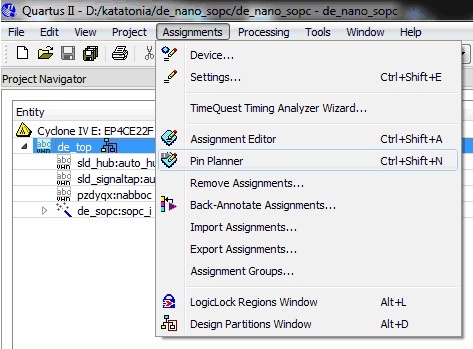

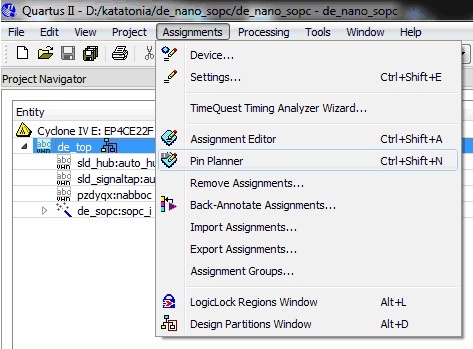

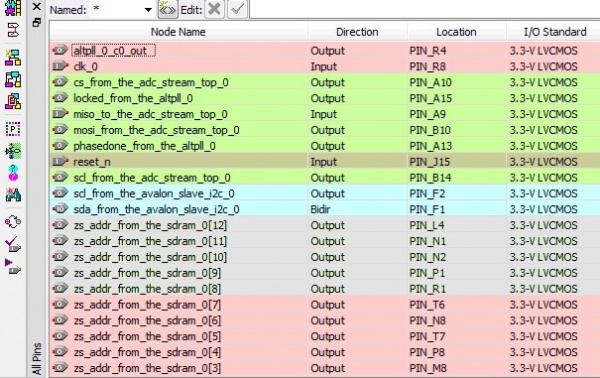

Большинство портов относится к SDRAM памяти, для которой помимо сигналов адреса, данных и т.д. выведен тактирующий сигнал от PLL. Все порты в заголовке выводятся на внешние контакты ПЛИС:

Разводку выводов по плате можно посмотреть в документации на DE0-nano. После компиляции имеем готовую прошивку. А также описание системы на кристалле в формате .sopcinfo. Это файл будет использоваться в дальнейшем при создании программно обеспечения в среде Nios II 10.1 Software Build Tools for Eclipse.

5 комментариев