BrainfuckPC#12 Итоги 2017 года и планы на 2018

Закрываем 2017-й год грандиозными итогами года и амбициозными планами на следующий год

Итоги:

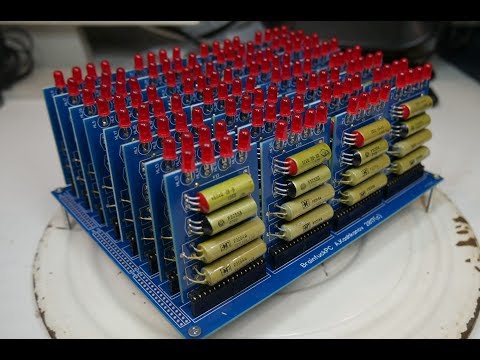

1. Плата памяти собрана, но хочу переделать

2. Блок сумматора собран, нужно тестировать

3. Модули индикации и защелок разработаны, надо собирать остальные

Планы:

1. Продолжаем сборку релейного компьютера:

a. Проверить сумматор

b. Собрать все индикаторы, защелки

c. Собрать регистры

d. Собрать логику

e. Прошить плату памяти и индикаторные платы

f. Разобраться с корпусом

2. Провести эксперименты с декатронами

3. Открыть раздел «книжная полка»

4. Поиграться со струйной логикой

5. Обзавестись лазерным гравером

6. Продолжить цикл по мехатронике и начать собирать всякое движимое и вращаемое

Итоги:

1. Плата памяти собрана, но хочу переделать

2. Блок сумматора собран, нужно тестировать

3. Модули индикации и защелок разработаны, надо собирать остальные

Планы:

1. Продолжаем сборку релейного компьютера:

a. Проверить сумматор

b. Собрать все индикаторы, защелки

c. Собрать регистры

d. Собрать логику

e. Прошить плату памяти и индикаторные платы

f. Разобраться с корпусом

2. Провести эксперименты с декатронами

3. Открыть раздел «книжная полка»

4. Поиграться со струйной логикой

5. Обзавестись лазерным гравером

6. Продолжить цикл по мехатронике и начать собирать всякое движимое и вращаемое