Фоновая подсветка HDMI-FPGA-LED. Часть 2: Альтернатива

«На Почту России надейся, а сам не плошай» или альтернативный путь развития проекта HDMI-FPGA-LED и первые успешные попытки приема HDMI/DVI сигналов на FPGA.

Погуглив нашел, что на SeeedStudio.com предлагают не дорогой сервис по изготовления двухслойных печатных плат. По отзывам, качество печатных плат на выходе достойное, правда срок изготовления с доставкой ~1 месяц.

Заказал 19 мая 2013, изготовили, быстро — 5 дней, и настала замечательная пара ожидания когда же платы доберутся до России. На момент публикации топика, платы, а вместе с ними и программатор для Xilinx, были еще где-то в пути.

Таким образом рассказать о монтаже компонентов и первом включении не получится, будет в следующей части, надеюсь.

Ответ на вопрос «чем прошивать/отлаживать?», временно, пропустим.

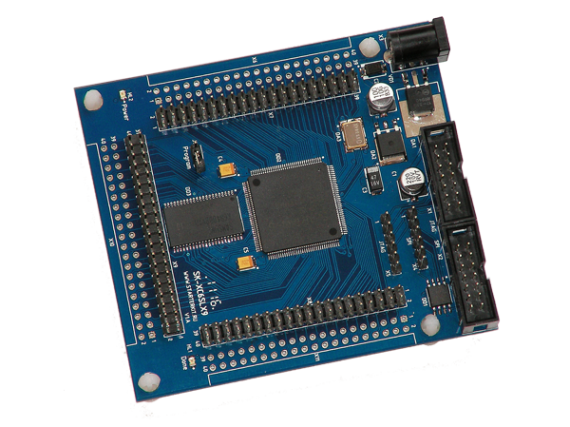

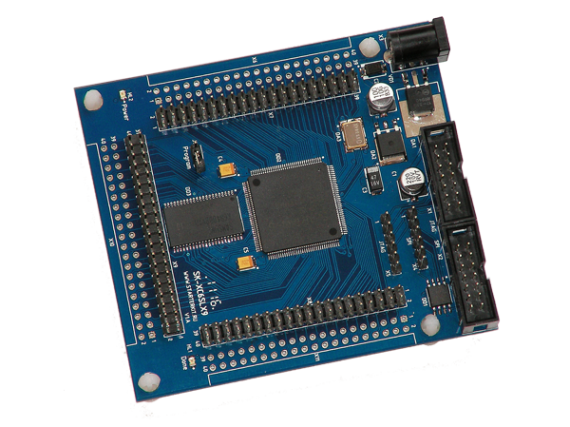

В качестве отладочной платы решил использовать отладку от starterki.ru, а именно SK-XC6SLX9.

Отладка крайне минималистична:

Примеров описания VGA для FPGA в интернете превеликое множество (1, 2, 3 и наконец google.com) для разных языков описания схем, да и к тому же там ничего сложного то и нет, поэтому свой код приводить пока не буду.

Собрав все в кучу, получилось следующее (извиняюсь за качество фото):

Картинка стабильна, цветопередача почти соответствует желаемому, несмотря на то, что я по не внимательности, младший бит красного цвета посадил на +3,3 В.

Видно, что по HDMI, помимо видео потока (TMDS channel 0/1/2/clk), передаются еще и данные по интерфейсам DDC и CEC, последний нас пока интересовать не будет. DDC есть не что иное как интерфейс I2C, только без мультимастера, мастер только один — источник видео сигнала. Основной информацией передаваемой по DDC, для случая не защищенного HDCP HDMI канала, является EDID — «это стандарт формата данных VESA, который содержит базовую информацию о мониторе и его возможностях, включая информацию о производителе, максимальном размере изображения...». Да и еще одна маленькая, но важная особенность: без получения «нормального» EDID, источник сигнала не активизирует передачу видео сигналов по TMDS. По итогу имеем следующее: приемником HDMI является FPGA которая и знать не знает что такое I2C, EDID, DDC, также для I2C есть схемотехнические особенности не позволяющие так просто FPGA воткнуть на эту шину, а без нормального EDID, честных сигналов TMDS от видеокарты не видать «как своих ушей». Писать дизайн I2C/DDC, EDID для FPGA сейчас совсем нет желания. Решил облегчить себе задачу, подсунув (временно) источнику видеосигнала, DDC с EDID от реального монитора, а TMDS благополучно завести на FPGA, где его уже и преобразовывать в RGB-цвет для каждого пикселя, который легко перекинуть в сигналы VGA. Звучит, наверное, сложно и запутанно, но это все работает (извиняюсь за качество фото):

Причина потери качества картинки на мониторе — однобитность DAC т.е. они здесь вообще не используются, на VGA уходит только старший бит каждого цвета.

CadSoft

SeeedStudio.com Fusion PCB Service

Печатная плата

В прошлом топике никак не была освещена тема разводки печатной платы, и если честно я не большой специалист в этих вопросах, но кое-что получилось.Разводка

При разводке печатной платы решил идти по пути наименьшего сопротивления и сделал все в EagleCAD 6.1.0. Библиотеки многих элементов доступны на сайте CadSoft. По причине не законченности устройства разводку печатной платы здесь не привожу. 3D вид на на плату, подготовленный в SketchUp 8 с использованием плагина EagleUp для EagleCAD:

Изготовление

Первоначальное изготовление печатной платы планировалось произвести в кустарных условиях используя ЛУТ, переходные отверстия заделать проводком МГТФ и т.д., но после того как оказалось что количество переходных отверстий более 50 и толщина дорог на пределе + начал «темнить» мой принтер, от использования ЛУТ пришлось отказаться.Погуглив нашел, что на SeeedStudio.com предлагают не дорогой сервис по изготовления двухслойных печатных плат. По отзывам, качество печатных плат на выходе достойное, правда срок изготовления с доставкой ~1 месяц.

Заказал 19 мая 2013, изготовили, быстро — 5 дней, и настала замечательная пара ожидания когда же платы доберутся до России. На момент публикации топика, платы, а вместе с ними и программатор для Xilinx, были еще где-то в пути.

Таким образом рассказать о монтаже компонентов и первом включении не получится, будет в следующей части, надеюсь.

Альтернативы

Не смотря на то, что, ни плат ни программатора не было, проект продолжать надо, а значит нужно решить 2 проблемы: что прошивать (FPGA есть, а платы под него нет), и чем прошивать/отлаживать.Ответ на вопрос «чем прошивать/отлаживать?», временно, пропустим.

В качестве отладочной платы решил использовать отладку от starterki.ru, а именно SK-XC6SLX9.

Отладка крайне минималистична:

- Xilinx FPGA Spartan 6 — XC6SLX9

- SRAM 512K

- Генератор 50МГц

- 2 LDO

- Диод от переполюсовки

- Flash AT45DB021

Hellow VGA

Так как на SK-XC6SLX9 нет ни светодиодов доступных пользователю, ни кнопок, то от привычного Hellow Led отказался в пользу Hellow VGA. Тем более, VGA выход понадобится, чтобы убедиться в корректности принимаемого по HDMI видео потока. На коленке развел-спаял плату с парой кнопок и светодиодов, а также с тремя четырех битными ЦАП по схеме R2R (если окончание фразы оказалось слишком запутанным — вот ссылка для ознакомления).Примеров описания VGA для FPGA в интернете превеликое множество (1, 2, 3 и наконец google.com) для разных языков описания схем, да и к тому же там ничего сложного то и нет, поэтому свой код приводить пока не буду.

Собрав все в кучу, получилось следующее (извиняюсь за качество фото):

Картинка стабильна, цветопередача почти соответствует желаемому, несмотря на то, что я по не внимательности, младший бит красного цвета посадил на +3,3 В.

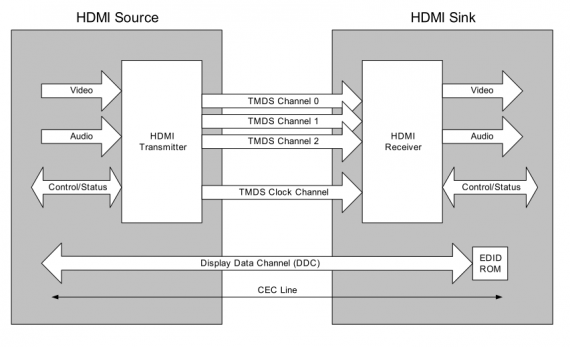

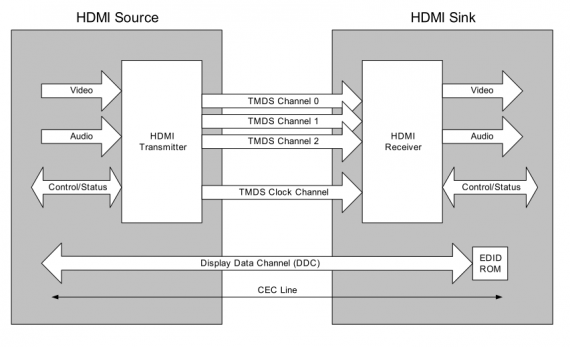

Галопом по Европам: Hellow TMDS

Провека работоспособности механизма преобразование HDMI/DVI в RGB для каждого пикселя дисплея, будет осуществляться по связке Ноутбук->HDMI->FPGA->VGA->Монитор. Для преобразования HDMI->FPGA понадобятся теоретические (читай как поверхностные) знания стандарта HDMI 1.3, в котором имеется следующая, крайне познавательная, картинка:

Видно, что по HDMI, помимо видео потока (TMDS channel 0/1/2/clk), передаются еще и данные по интерфейсам DDC и CEC, последний нас пока интересовать не будет. DDC есть не что иное как интерфейс I2C, только без мультимастера, мастер только один — источник видео сигнала. Основной информацией передаваемой по DDC, для случая не защищенного HDCP HDMI канала, является EDID — «это стандарт формата данных VESA, который содержит базовую информацию о мониторе и его возможностях, включая информацию о производителе, максимальном размере изображения...». Да и еще одна маленькая, но важная особенность: без получения «нормального» EDID, источник сигнала не активизирует передачу видео сигналов по TMDS. По итогу имеем следующее: приемником HDMI является FPGA которая и знать не знает что такое I2C, EDID, DDC, также для I2C есть схемотехнические особенности не позволяющие так просто FPGA воткнуть на эту шину, а без нормального EDID, честных сигналов TMDS от видеокарты не видать «как своих ушей». Писать дизайн I2C/DDC, EDID для FPGA сейчас совсем нет желания. Решил облегчить себе задачу, подсунув (временно) источнику видеосигнала, DDC с EDID от реального монитора, а TMDS благополучно завести на FPGA, где его уже и преобразовывать в RGB-цвет для каждого пикселя, который легко перекинуть в сигналы VGA. Звучит, наверное, сложно и запутанно, но это все работает (извиняюсь за качество фото):

Причина потери качества картинки на мониторе — однобитность DAC т.е. они здесь вообще не используются, на VGA уходит только старший бит каждого цвета.

В место заключения

В следующей части:- Очень поверхностное описание алгоритма приема TMDS сигналов на FPGA семейства Spartan 6;

- Содержание EDID и как/где его взять;

- I2C/DDC на FPGA;

- HDMI to LED.

Ссылки

Почта РоссииCadSoft

SeeedStudio.com Fusion PCB Service

16 комментариев

А зачем VGA вообще? По-моему, первое, что нужно сделать — прокси HDMI. А потом, уже и шпионить за шиной :)

VGA нужен исключительно для отладки и проверки стабильности принимаемого видео сигнала.

PS bsvi — опередил :)

Вы не подумайте, что я пытаюсь умничать или доколупаться, мне интересен факт сколько может занять работа над HDMI core с нуля, если сесть и работать только над ним?

Сложно оценить, много факторов. Я все делал по аналогии с Application Note: Video Connectivity Using TMDS I/O in Spartan-3A FPGAs и Implementing a TMDS Video Interface in the Spartan-6 FPGA, поэтому все заняло не очень много времени, ~2-3 недели

Видео меня не очень интересует, но вот возможность выдернуть звук из HDMI меня заинтересовала…

Очень хотелось бы собрать девайс для подключения многоканального звука с разных цифровых источников (оптика, коаксил, HDMI, можно и АЦП) с возможностью обрабатывать каждый канал каждого источника, смешивать их, включать/выключать по отдельности и выводить все это дело также в цифровом виде на несколько каналов. Управлять через UART или Ethernet. Собираю информацию…

На борту на ВХОД: HDMI, VGA, Analog Composite. На выходе LVDS и монитор TTL, к ним и цепляем ПЛИС.

Вам понравилась моя идея? www.aliexpress.com/item/HDMI-VGA-2AV-Reversing-Driver-board-7inch-AT070TN90-800-480-lcd-display/638642446.html

hamsterworks.co.nz/mediawiki/index.php/Dvid_test