Связка Altium Designer и HyperLynx. - Часть 1. Моделирование целостности сигналов в Altium.

Иногда возникает необходимость разработки радиоэлектронных изделий, в которых используются высокоскоростные интерфейсы (например, модули быстрой памяти (DDR2), микросхемы выработки сигналов физического уровня (USB 2.0, Ethernet), быстрые АЦП, микросхемы видео и т.д.).

Трассировка данных компонентов самих по себе обычно не представляет сложностей, подробно описана в соответствующих datasheet'ах и примерах отладочных плат. Однако, при разработке сложного устройств, сложного стека печатной платы и необычных конфигурациях соединения микросхем — оценка качества разводки без специализированных средств представляется мало возможной Вот здесь на помощь и приходят средства моделирования целостности сигналов.

Одним из наиболее распространенных и могучих средств является пакет HyperLynx от Mentor Graphics, который (не без костылей) можно подружить с Altium.

Статья не претендует на полноценное руководство по моделированию целостности сигналов. По сути, разбирается один пример и два способа решения задачи. Возможно, более сложную инструкцию напишу позже.

Более подробная информация о моделировании целостности сигналов может быть получена на английском языке в (Signal Integrity).

— Altium Designer

— .ibis модели компонентов, которые хотим промоделировать

— Какой-нибудь калькулятор импеданса (напр. Agilent AppCAD)

Принципиальная схема изображена на рис.1.

Рис. 1. Схема принципиальная

Обратите внимание на то, что выводам УГО, которые будут моделироваться, назначен необходимый тип (Input, Output или I/O в соответствии со спецификацией).

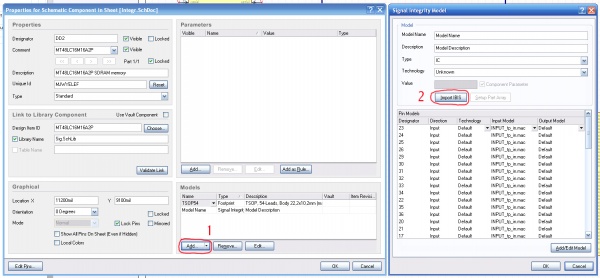

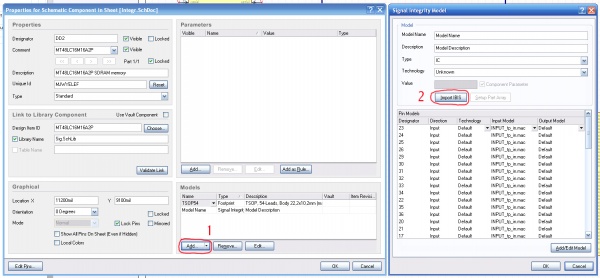

Соответствующая модель IBIS, описывающая основные электрические характеристики буфера входа или выхода микросхемы может быть назначена компоненту через меню настроек и импорта IBIS (двойной щелчок на компоненте в редакторе моделей, область Models -> Add -> Signal Integrity -> Import IBIS (см. рис. 2)).

Рис. 2. Импорт модели IBIS для соответствующего электронного компонента

В повившемся окне «Ibis Converter» выбираем модель, соответствующую нашему компоненту.

На выходе получим отчет, описывающий результат сопоставления моделей соответствующим выводам компонент в формате:

Matching IBIS pin: 37 with model: INPUT_tp_in.mac.

Matching IBIS pin: 2 with model: DQ_tp_out.mac.

Matching IBIS pin: 4 with model: DQ_tp_out.mac.

Any unmatched IBIS pins should have their model/technology set manually.

После чего в области «Pin Models» в зависимости от направления работы вывода можно назначить или модифицировать модель.

К сожалению, Altium очень плохо поддерживает секцию Model Selector в файле Ibis. Данная секция описывает параметры вывода в зависимости от дополнительных условий — наличия pull-up, pull-down и т.д. Поэтому нередко приходится перекраивать модель под себя, чему, возможно, будет посвящен отдельный материал.

— Паяльная маска (15 мкм)

— Top (Медь — 35 мкм)

— Препрег (FR4 — 0,2 мм)

— Internal Plane 1 (Медь — 35 мкм)

— Ядро (FR4 — 0.8 мм)

— Internal Plane 2 (Медь — 35 мкм)

— Препрег (FR4 — 0,2 мм)

— Bottom (Медь — 35 мкм)

— Паяльная маска (15 мкм)

Рис. 3. Вид стека и формула расчета импеданса

Использование Plane во внутренних слоях обязательно для корректного расчета импеданса.

Форма и параметры тестового сигнала (Stumulus) может быть задана через Design Rules (Design -> Rules -> Signal Integrity -> Stimulus).

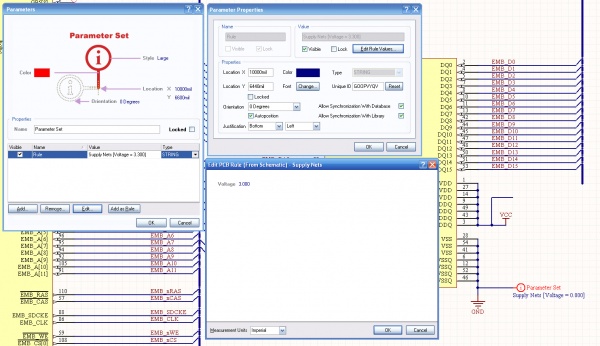

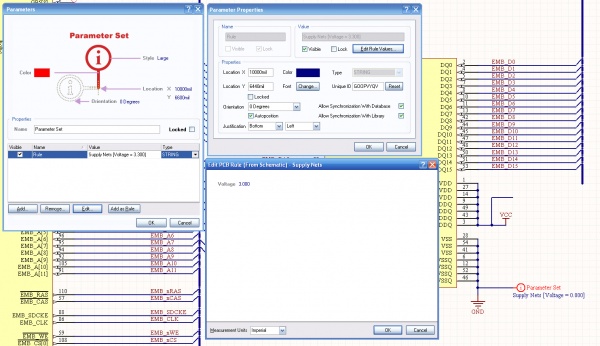

Уровни напряжения микросхемы (для корректной работы модели) могут быть настроены при помощи директив в схемотехническом редакторе (Place -> Directives -> Parameter Set, где Add As A Rule -> Edit Rule Values -> Supply Nets) (см. Рис. 4).

Рис. 4. Настройка напряжения питания через Parameter Set

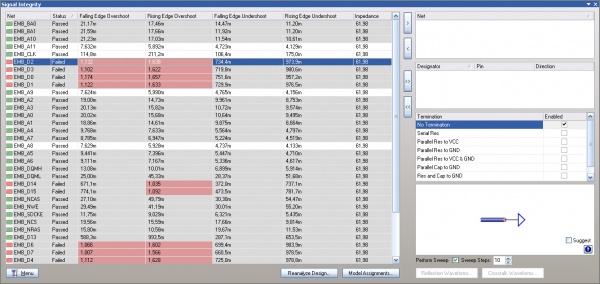

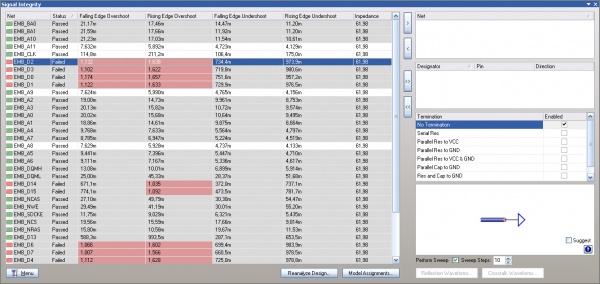

Перейдем в схемотехническом редакторе в окно настройки параметров моделирования (Tools -> Signal Integrity), рис. 5.

Рис. 5. Окно Signal Integrity

Нажимаем кнопку Reanalize Design в нижней части окна для получения информации о доступных моделях.

Данное окно предоставляет информацию о цепях, моделирование которых возможно произвести.

В нижнем левом углу кнопка Menu позволяет настроить отображение полей вывода информации (Menu -> Show/Hide Columns), параметры моделирования (Menu -> Preferences), параметры настройки допуска по напряжению сигналов для проверки «на лету» (Menu -> Set Tolerances).

Цепи, имя которых окрашено серым цветом — физически не разведены и для них возможнен лишь предтопологический анализ. Цепи, имя которых окрашено белым — разведены и для них возможнет посттопологический анализ (т.е. учет физических параметров проводника, соединяющего выводы микросхем).

Непосредственно моделирование цепи с выводом графика просходит путем добавления её в список Nets (двойным щелчком на названии цепи либо нажатием на кропку [>]).

В правом нижнем рабочем поле при необходимости можно настроить параметры терминирования сигналов при использовании последовательно подключенных резисторов, подтяжек к напряжению питания или земле или использования диодов Шоттки.

Кнопка Perform Sweep позволяет промоделировать поведение цепи при нескольких номиналах терминирующих элементов. Sweep Steps позволяет задать количество шагов при моделировании.

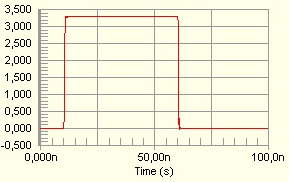

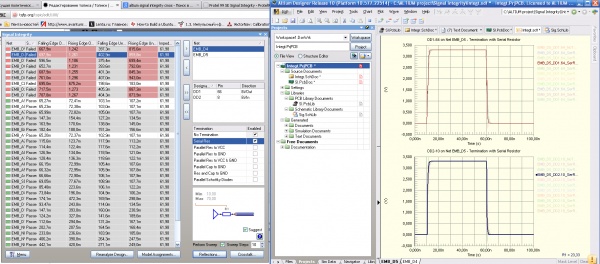

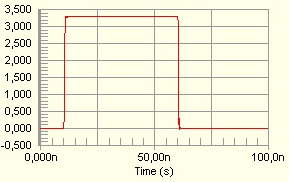

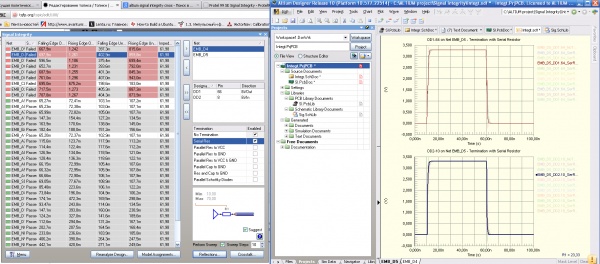

Простое моделирование формы сигнала доступно при нажатии на кнопку «Reflection Waveforms» (рис. 6)

Результаты моделирования отображаются в виде двух семеств графиков. При нажатии на легенду в прявой части графика подствечивается кривые, полученные при соответствующих номиналах терминируюхиэ элементов. Таким образом, можно расчитать, например, минимально необходимый номинал резистора для достижения минимального перерегулирования.

Рис. 6. Результаты моделирования Reflection Waveforms

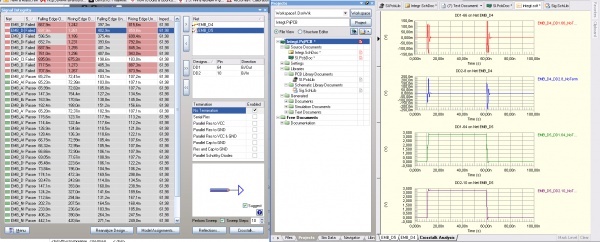

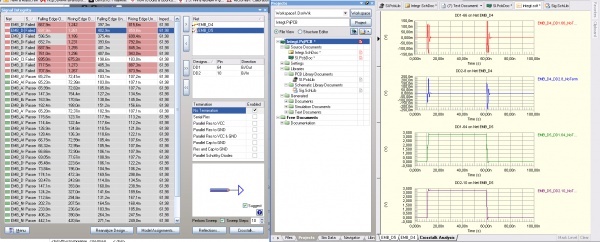

Похожим образом можно промоделировать взаимное влияние цепей друг на друга. Для этого необходимо добавить больше одной цепи в список Nets. Нажать правой клавишей на необходимую цепь и выбрать её роль — «жертва» (Set Victim) либо «агрессор» (Set Agressor). После чего оценить взаимное влияние цепей нажатием на кнопку Crosstalk. В верхней части графика можно увидеть значение напряжения на входах/выходах исследуемых электронных компонентов.

Рис. 7. Результаты моделирования Crosstalk

В следующих частях мы разберем особенности экспорта в HyperLynx и научимся основным навыкам работы с данным пакетом.

Архив проекта и .ibis могут быть скачаны с yadi.sk/d/BgFQSDqj3A7xT

Трассировка данных компонентов самих по себе обычно не представляет сложностей, подробно описана в соответствующих datasheet'ах и примерах отладочных плат. Однако, при разработке сложного устройств, сложного стека печатной платы и необычных конфигурациях соединения микросхем — оценка качества разводки без специализированных средств представляется мало возможной Вот здесь на помощь и приходят средства моделирования целостности сигналов.

Одним из наиболее распространенных и могучих средств является пакет HyperLynx от Mentor Graphics, который (не без костылей) можно подружить с Altium.

Статья не претендует на полноценное руководство по моделированию целостности сигналов. По сути, разбирается один пример и два способа решения задачи. Возможно, более сложную инструкцию напишу позже.

Более подробная информация о моделировании целостности сигналов может быть получена на английском языке в (Signal Integrity).

Что мы хотим получить?

Математическую модель радиоэлектронного модуля, которая позволила бы промоделировать процесс распространения сигналов между выводами электронных компонентов по печатной плате заданного стека.Что нам нужно?

— Mentor Graphics HyperLynx— Altium Designer

— .ibis модели компонентов, которые хотим промоделировать

— Какой-нибудь калькулятор импеданса (напр. Agilent AppCAD)

Исходные данные

В качестве примера разберем анализ сигналов линий SDRAM микросхемы памяти MT48LC16M16A2P при подключении к цифровому сигнальному процессору TMS320C6745.Принципиальная схема изображена на рис.1.

Рис. 1. Схема принципиальная

Обратите внимание на то, что выводам УГО, которые будут моделироваться, назначен необходимый тип (Input, Output или I/O в соответствии со спецификацией).

Соответствующая модель IBIS, описывающая основные электрические характеристики буфера входа или выхода микросхемы может быть назначена компоненту через меню настроек и импорта IBIS (двойной щелчок на компоненте в редакторе моделей, область Models -> Add -> Signal Integrity -> Import IBIS (см. рис. 2)).

Рис. 2. Импорт модели IBIS для соответствующего электронного компонента

В повившемся окне «Ibis Converter» выбираем модель, соответствующую нашему компоненту.

На выходе получим отчет, описывающий результат сопоставления моделей соответствующим выводам компонент в формате:

Matching IBIS pin: 37 with model: INPUT_tp_in.mac.

Matching IBIS pin: 2 with model: DQ_tp_out.mac.

Matching IBIS pin: 4 with model: DQ_tp_out.mac.

Any unmatched IBIS pins should have their model/technology set manually.

После чего в области «Pin Models» в зависимости от направления работы вывода можно назначить или модифицировать модель.

К сожалению, Altium очень плохо поддерживает секцию Model Selector в файле Ibis. Данная секция описывает параметры вывода в зависимости от дополнительных условий — наличия pull-up, pull-down и т.д. Поэтому нередко приходится перекраивать модель под себя, чему, возможно, будет посвящен отдельный материал.

Предтопологический анализ

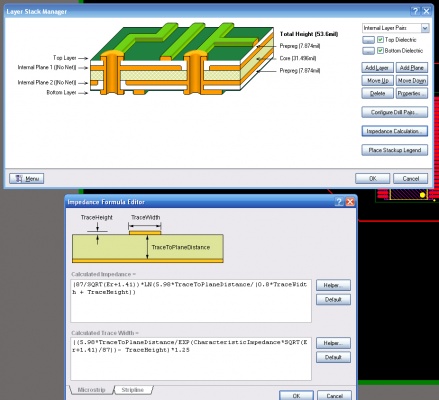

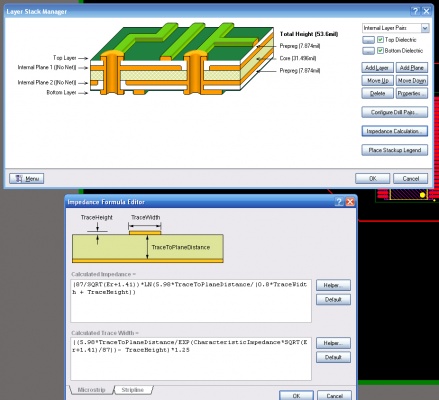

Рассмотрим пример предтопологического анализа сигналов для следующего стека печатной платы (настраивается Design -> Layer Stack Manager) (рис. 3):— Паяльная маска (15 мкм)

— Top (Медь — 35 мкм)

— Препрег (FR4 — 0,2 мм)

— Internal Plane 1 (Медь — 35 мкм)

— Ядро (FR4 — 0.8 мм)

— Internal Plane 2 (Медь — 35 мкм)

— Препрег (FR4 — 0,2 мм)

— Bottom (Медь — 35 мкм)

— Паяльная маска (15 мкм)

Рис. 3. Вид стека и формула расчета импеданса

Использование Plane во внутренних слоях обязательно для корректного расчета импеданса.

Форма и параметры тестового сигнала (Stumulus) может быть задана через Design Rules (Design -> Rules -> Signal Integrity -> Stimulus).

Уровни напряжения микросхемы (для корректной работы модели) могут быть настроены при помощи директив в схемотехническом редакторе (Place -> Directives -> Parameter Set, где Add As A Rule -> Edit Rule Values -> Supply Nets) (см. Рис. 4).

Рис. 4. Настройка напряжения питания через Parameter Set

Перейдем в схемотехническом редакторе в окно настройки параметров моделирования (Tools -> Signal Integrity), рис. 5.

Рис. 5. Окно Signal Integrity

Нажимаем кнопку Reanalize Design в нижней части окна для получения информации о доступных моделях.

Данное окно предоставляет информацию о цепях, моделирование которых возможно произвести.

В нижнем левом углу кнопка Menu позволяет настроить отображение полей вывода информации (Menu -> Show/Hide Columns), параметры моделирования (Menu -> Preferences), параметры настройки допуска по напряжению сигналов для проверки «на лету» (Menu -> Set Tolerances).

Цепи, имя которых окрашено серым цветом — физически не разведены и для них возможнен лишь предтопологический анализ. Цепи, имя которых окрашено белым — разведены и для них возможнет посттопологический анализ (т.е. учет физических параметров проводника, соединяющего выводы микросхем).

Непосредственно моделирование цепи с выводом графика просходит путем добавления её в список Nets (двойным щелчком на названии цепи либо нажатием на кропку [>]).

В правом нижнем рабочем поле при необходимости можно настроить параметры терминирования сигналов при использовании последовательно подключенных резисторов, подтяжек к напряжению питания или земле или использования диодов Шоттки.

Кнопка Perform Sweep позволяет промоделировать поведение цепи при нескольких номиналах терминирующих элементов. Sweep Steps позволяет задать количество шагов при моделировании.

Простое моделирование формы сигнала доступно при нажатии на кнопку «Reflection Waveforms» (рис. 6)

Результаты моделирования отображаются в виде двух семеств графиков. При нажатии на легенду в прявой части графика подствечивается кривые, полученные при соответствующих номиналах терминируюхиэ элементов. Таким образом, можно расчитать, например, минимально необходимый номинал резистора для достижения минимального перерегулирования.

Рис. 6. Результаты моделирования Reflection Waveforms

Похожим образом можно промоделировать взаимное влияние цепей друг на друга. Для этого необходимо добавить больше одной цепи в список Nets. Нажать правой клавишей на необходимую цепь и выбрать её роль — «жертва» (Set Victim) либо «агрессор» (Set Agressor). После чего оценить взаимное влияние цепей нажатием на кнопку Crosstalk. В верхней части графика можно увидеть значение напряжения на входах/выходах исследуемых электронных компонентов.

Рис. 7. Результаты моделирования Crosstalk

В следующих частях мы разберем особенности экспорта в HyperLynx и научимся основным навыкам работы с данным пакетом.

Архив проекта и .ibis могут быть скачаны с yadi.sk/d/BgFQSDqj3A7xT

6 комментариев

Насколько я понял, предтопологический анализ подразумевает, что ножки микросхем соединены непосредственно, а посттополочиеский уже учитывает плату, правильно?

Его длина и импеданс настраиваются через Menu -> Setup Options окна Signal Integrity (т.е. для всех неразведенных проводников задается длина и импеданс). Ширина соответствует Preffered для Top.

Для разведенных проводников импеданс расчитывается по формуле (рис.3 статьи):

(87/SQRT(Er+1.41))*LN(5.98*TraceToPlaneDistance/(0.8*TraceWidth + TraceHeight)

Ширина соответствует Prefered Width в Design Rules для соответствующего слоя.

Толщина, расстояние до опорного слоя земли/питания и диэлектрическая проницаемость настраиваются в Layer Stack Manager.

Параметры входных/выходных буферов соответствуют модели в .ibis и не зависят от того — разведен ли проводник или нет.

Можете ради эксперимента изменить Preferred толщину проводников на Top Layer с 10 до 20 mil.

После чего, нажав Reanalyze design… в окне Signal Integrity увидим, что импеданс неразведенных линий изменился с 61,98 до 42,24 Ом.