Связка Altium Designer и HyperLynx. - Часть 2. Экспорт в Hyperlynx и работа в нем.

Вторая часть статьи о моделировании целостности сигнала.

В статье кратко описаны нюансы экспортирования файлов в Hyperlynx, их открытие и дан пример моделирования целостности некоторой сигнальной линии.

IBIS (input/output buffer information specification) формат описания моделей входных и выходных буферов интегральных схем. Он широко распространен в пакетах моделирования целостности сигналов и по сути является единым универсальным форматом.

IBIS модель может включать в себя физические характеристики вывода исследуемой микросхемы и его электрические характеристики.

К физическим характеристикам относятся сопротивление R, емкость C и индуктивность L вывода.

К электрическим характеристикам относятся вольт-амперные характеристики, заданные в табличном виде для режимов нормальной работы (входной уровень сигнала лежит в диапазоне от напряжения «земли» (GND) до напряжения питания (VDD)), при напряжении на входе выше максимально возможного напряжения логической единицы [т.н. режим Power Clamp] и при напряжении на входе ниже напряжения логического нуля [т.н. режим Ground Clamp].

Более подробное описание IBIS может быть найдено, например, в документе «TI IBIS File Creation, Validation, and Distribution Processes» (szza034).

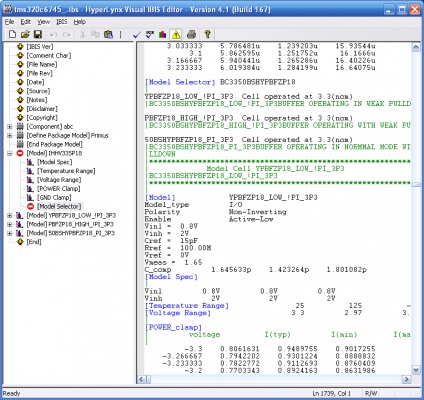

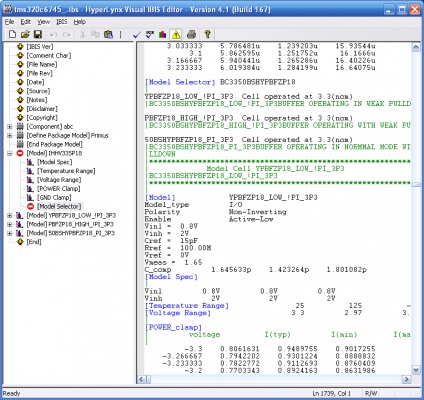

Крайне удобным инструментом для просмотра и моделирования IBIS-файлов является Visual IBIS Editor, поставляемый вместе с пакетом HyperLynx.

В случае несоответствия модели Ibis используемым в пакете моделирования целостности — несоответствия будут подчеркиваться символом — красным крестом (см. рис. 1).

Рис. 1. Внешний вид Visual IBIS Editor.

На скриншоте видно, что оператор [Model Selector] не соответствует используемой спецификации IBIS.

Конструкция

[Model Selector] BC3350BSHYPBFZP18

YPBFZP18_LOW_!PI_3P3 Cell operated at 3.3(nom)

|BC3350BSHYPBFZP18_LOW_!PI_3P3BUFFER OPERATING IN WEAK PULLDOWN MODE

PBFZP18_HIGH_!PI_3P3 Cell operated at 3.3(nom)

|BC3350BSHYPBFZP18_HIGH_!PI_3P3BUFFER OPERATING WITH WEAK PULLUP ON

50BSHYPBFZP18_PI_3P3 Cell operated at 3.3(nom)

|BC3350BSHYPBFZP18_PI_3P3BUFFER OPERATING IN NORMMAL MODE WITHOUT PULLUP/PULLDOWN

означает, что при моделировании схемы с Pulldown будет использоваться (BC3350BSHYPBFZP18_LOW_!PI_3P3BUFFER), с Pullup — (PBFZP18_HIGH_!PI_3P3), без подтяжки — (BC3350BSHYPBFZP18_PI_3P3BUFFER).

Единственным возможным вариантом обеспечить работоспособность модели в Altium — жесткой автозаменой заменить имя, соответствующее Model Selector (напр. BC3350BSHYPBFZP18) на модель, используемую в соответствии со схемой (напр. BC3350BSHYPBFZP18_PI_3P3BUFFER). В Hyperlynx такой шаманизм не требуется — необходимые модели подцепляются автоматически.

Прямой экспорт у меня не заработал (Build 10.577.22514). Вернее, экспортировать — экспортируется, но с огромныыми глюками. Поэтому воспользуемся двухступенчатым экспортом.

Этап 1.

Сначала экспортируем файл трассировки (.pcb) из Altium в Specctra Design File (.dsn) через File -> Save as… -> Export Specctra Design File (.dsn).

Настройки экспорта оставляем по умолчанию.

Этап 2.

Импорт трассировки из .dsn в Hyperlynx через File -> New Board (Run PCB Translator).

В появившемся окне нажимаем кнопку «Translate & Open».

В окне Restore Session Edits ставим все галочки и выбираем пункт Previous в «Session to restore».

Предупреждения о неразведенных цепях игноррируем (Close в окне предупреждения).

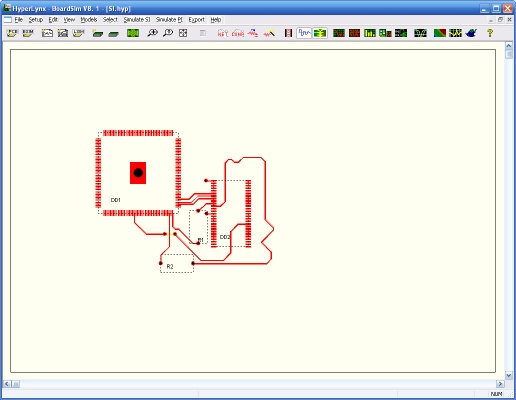

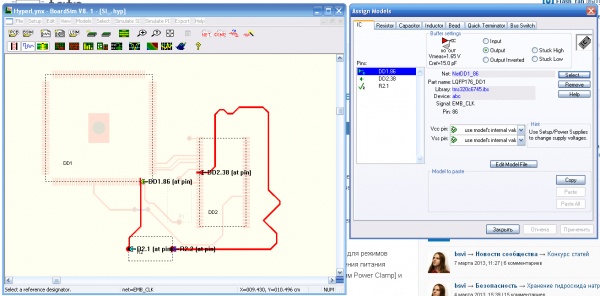

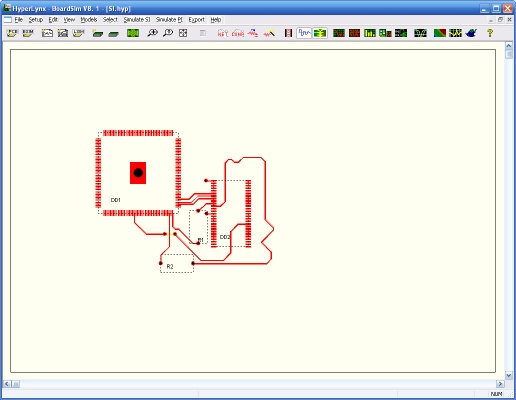

Внешний вид топологии показан на рис. 2.

Рис. 2. Внешний вид топологии печатной платы

Этап 3.

Все файлы моделей в формате .ibs, с которыми нам предстоит работать необходимо поместить в папку [директория установки HyperLynx]\2010HL\SDD_HOME\hyperlynx\Libs.

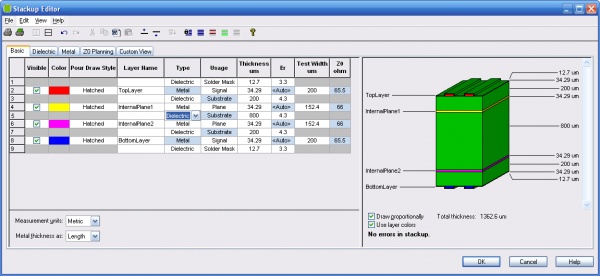

В первую очередь необходимо настроить стек печатной платы в соответствии с нашим стеком в Altium.

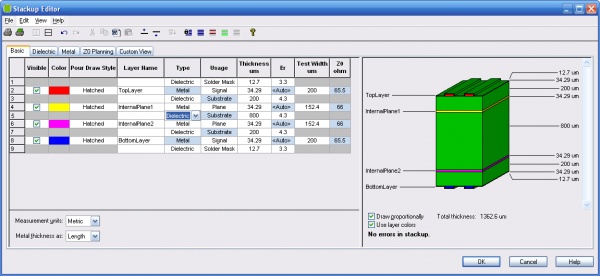

Нажмем в верхнем меню Setup -> Stackup -> Edit… (рис. 3)

В появившемся окне Stackup Editor добавим недостающее количество слоев нажав правой клавишей на существующих строчках и Insert Above/Below -> Signal/Solid Plane/Substate (Сигнальный слой/Опорный слой/Диэлектрик) и настроим их толщины (колонка Thickness).

Верхние вкладки (Basic… Dielectric… Metal… Z0) позвлдяют перестроить таблицу стека печатной платы наиболее удобным образом для конкретных задач. Например, вкладка Z0 позволяет вбить значение импеданса для необходимого слоя, — и автоматически расчитать ширину проводника для достижения необходимого импеданса.

Рис. 3. Внешний вид Stackup Editor

Сопоставление моделей

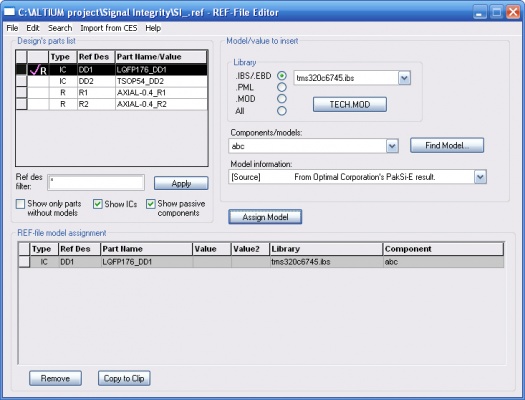

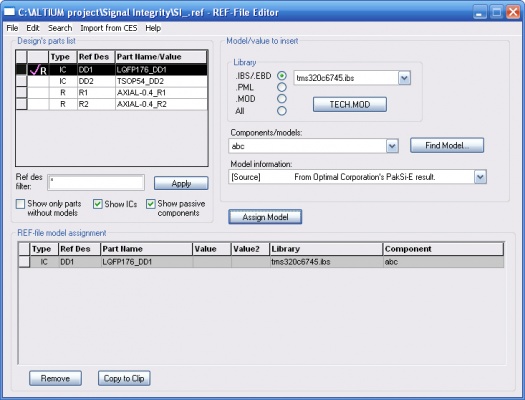

Далее — назначим компонентам схемы соответствующие модели. Наиболее простым способом это можно сделать через меню Models -> Assign Models/Values by Reference Designators (.REF file).

В появившемся окне можно сопоставить обозначению компонента модель либо изменить параметр (для простых пассивных компонентов) (см. рис. 4.).

Для сопоставления необходимо выбрать наименование компонента в рабочей области «Design's part list», переключить круглую кнопку на .ibs в меню «Library» в правой части окна, из выпадающего списка выбрать необходимый файл модели и нажать «Assign». После чего — при благоприятном исходе сопоставления моделей — напротив наименования компонента появится зеленая галочка, символизирующая корректность сопоставление модели.

После окончания сопоставления всех моделей жмем Save для сохранения.

Рис. 4. Внешний вид окна REF-File editor

Редактирование параметров входа/выхода и тестового сигнала

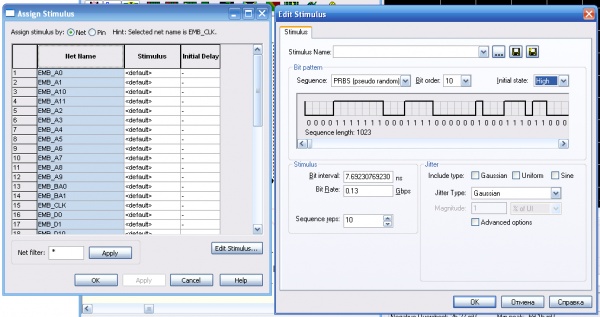

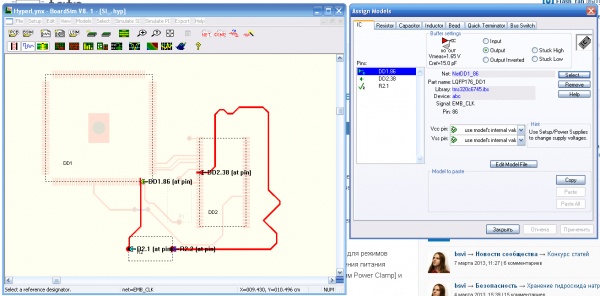

В качестве примера попробуем промоделировать сигнал по цепи EMB_CLK.

Выберем цепь по названию через меню Select -> Net by Name for SI analysis. После чего подкорректируем параметры назначенной модели через Models -> Assign Models/Values by Net. Т.к. линия CLK TMS320C6745 является двунаправленной, но в нашем случае она — выход, в рабочей области Buffer settings выбираем Output (рис. 5).

Рис.5. Настройка буфера на выход

В верхних вкладках Resistor...Bead можно вбить значения для пассивных элементов. Вкладка Quick Termination позволяет настроить терминацию выводов.

Моделирование и отображение при помощи виртуального осциллографа

После того, как были выполнены все подготовитльные работы, перейдем непосредственно к моделированию.

Для этого через меню Simulate -> Run Interactive simulation (SI oscilloscope) запустим виртуальный осциллограф.

Его интерфейс интуитивно понятен. Остановимся лишь на некоторых моментах.

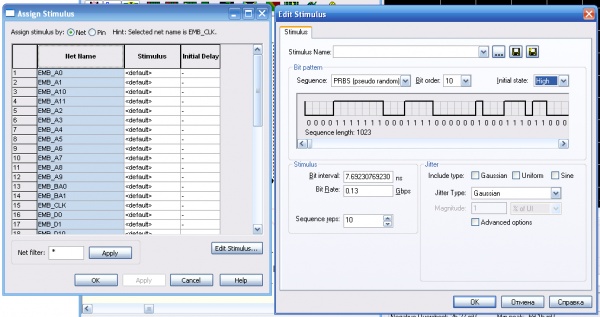

В рабочей области Stimulus установим круглую кнопку на пункт Per-Net/Pin и нажмем Assign… В появившемся меню для задания формы тестового сигнала нажмем Edit stimulus…

В качестве вида тестового сигнала выберем Pseudo-Random 10-го порядка. Количество повторений — 10. BitRate — 133 MHz (0.13 GBps). Для сохранения формы тестового сигнала нажмем на пиктограмму дискеты. (рис. 6) И сохраним в формате .eds.

В окне Assign Stimulus назначем сохраненный нами сигнал на цепь EMB_CLK.

Рис.6. Настройка формы тестового сигнала

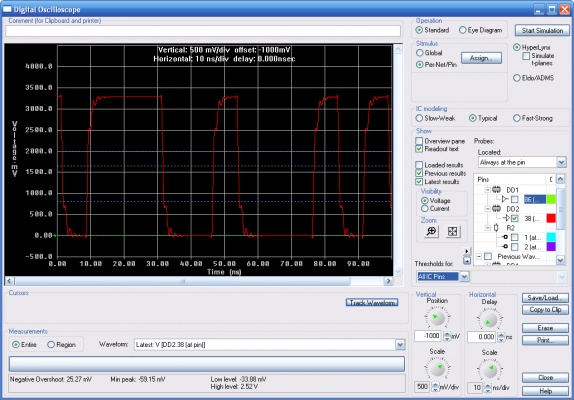

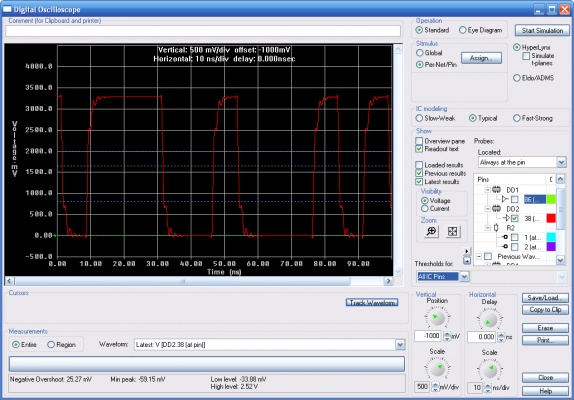

Видимость отображения графиков настраивается в рабочей области «Probes:» в правом углу окна «Digital Oscilloscope».

Удаление информации с рабочей области производится по нажатии кнопки Erase.

Маркеры в нижней части окна удобны для измерения величин (по времени и напряжению) промоделированного графика.

Начало моделирования выполняется по нажатии кнопки «Start Simulation». Результаты моделирования показаны на Рис.7.

Рис.7. Результаты моделирования

Моделирование перекрестных помех включается через меню основного окна Setup -> Enable Crosstalk Simulation. Параметры моделирования перекрестных помех настраиваются в меню Setup -> Crosstalk Thresholds (возможна настрока по величине перекрестных помех и по максимальной протяженности паралелльных проводников). При включении моделирования перекрестных помех в основном окне подсвечиваются цепи-агрессоры (проходящие по пороговым значениям перекрестных помех).

Исходный файл .dsn, полученный из него .hyp и модели можно скачать здесь

В статье кратко описаны нюансы экспортирования файлов в Hyperlynx, их открытие и дан пример моделирования целостности некоторой сигнальной линии.

Что такое IBIS и зачем он нужен?

IBIS (input/output buffer information specification) формат описания моделей входных и выходных буферов интегральных схем. Он широко распространен в пакетах моделирования целостности сигналов и по сути является единым универсальным форматом.

IBIS модель может включать в себя физические характеристики вывода исследуемой микросхемы и его электрические характеристики.

К физическим характеристикам относятся сопротивление R, емкость C и индуктивность L вывода.

К электрическим характеристикам относятся вольт-амперные характеристики, заданные в табличном виде для режимов нормальной работы (входной уровень сигнала лежит в диапазоне от напряжения «земли» (GND) до напряжения питания (VDD)), при напряжении на входе выше максимально возможного напряжения логической единицы [т.н. режим Power Clamp] и при напряжении на входе ниже напряжения логического нуля [т.н. режим Ground Clamp].

Более подробное описание IBIS может быть найдено, например, в документе «TI IBIS File Creation, Validation, and Distribution Processes» (szza034).

Крайне удобным инструментом для просмотра и моделирования IBIS-файлов является Visual IBIS Editor, поставляемый вместе с пакетом HyperLynx.

В случае несоответствия модели Ibis используемым в пакете моделирования целостности — несоответствия будут подчеркиваться символом — красным крестом (см. рис. 1).

Рис. 1. Внешний вид Visual IBIS Editor.

На скриншоте видно, что оператор [Model Selector] не соответствует используемой спецификации IBIS.

Конструкция

[Model Selector] BC3350BSHYPBFZP18

YPBFZP18_LOW_!PI_3P3 Cell operated at 3.3(nom)

|BC3350BSHYPBFZP18_LOW_!PI_3P3BUFFER OPERATING IN WEAK PULLDOWN MODE

PBFZP18_HIGH_!PI_3P3 Cell operated at 3.3(nom)

|BC3350BSHYPBFZP18_HIGH_!PI_3P3BUFFER OPERATING WITH WEAK PULLUP ON

50BSHYPBFZP18_PI_3P3 Cell operated at 3.3(nom)

|BC3350BSHYPBFZP18_PI_3P3BUFFER OPERATING IN NORMMAL MODE WITHOUT PULLUP/PULLDOWN

означает, что при моделировании схемы с Pulldown будет использоваться (BC3350BSHYPBFZP18_LOW_!PI_3P3BUFFER), с Pullup — (PBFZP18_HIGH_!PI_3P3), без подтяжки — (BC3350BSHYPBFZP18_PI_3P3BUFFER).

Единственным возможным вариантом обеспечить работоспособность модели в Altium — жесткой автозаменой заменить имя, соответствующее Model Selector (напр. BC3350BSHYPBFZP18) на модель, используемую в соответствии со схемой (напр. BC3350BSHYPBFZP18_PI_3P3BUFFER). В Hyperlynx такой шаманизм не требуется — необходимые модели подцепляются автоматически.

Экспорт из Altium в Hyperlynx

Из Altium возможен как прямой экспорт, так и через промежуточный формат .brd.Прямой экспорт у меня не заработал (Build 10.577.22514). Вернее, экспортировать — экспортируется, но с огромныыми глюками. Поэтому воспользуемся двухступенчатым экспортом.

Этап 1.

Сначала экспортируем файл трассировки (.pcb) из Altium в Specctra Design File (.dsn) через File -> Save as… -> Export Specctra Design File (.dsn).

Настройки экспорта оставляем по умолчанию.

Этап 2.

Импорт трассировки из .dsn в Hyperlynx через File -> New Board (Run PCB Translator).

В появившемся окне нажимаем кнопку «Translate & Open».

В окне Restore Session Edits ставим все галочки и выбираем пункт Previous в «Session to restore».

Предупреждения о неразведенных цепях игноррируем (Close в окне предупреждения).

Внешний вид топологии показан на рис. 2.

Рис. 2. Внешний вид топологии печатной платы

Этап 3.

Все файлы моделей в формате .ibs, с которыми нам предстоит работать необходимо поместить в папку [директория установки HyperLynx]\2010HL\SDD_HOME\hyperlynx\Libs.

Настройка моделей, основы моделирования

Настройка стекаВ первую очередь необходимо настроить стек печатной платы в соответствии с нашим стеком в Altium.

Нажмем в верхнем меню Setup -> Stackup -> Edit… (рис. 3)

В появившемся окне Stackup Editor добавим недостающее количество слоев нажав правой клавишей на существующих строчках и Insert Above/Below -> Signal/Solid Plane/Substate (Сигнальный слой/Опорный слой/Диэлектрик) и настроим их толщины (колонка Thickness).

Верхние вкладки (Basic… Dielectric… Metal… Z0) позвлдяют перестроить таблицу стека печатной платы наиболее удобным образом для конкретных задач. Например, вкладка Z0 позволяет вбить значение импеданса для необходимого слоя, — и автоматически расчитать ширину проводника для достижения необходимого импеданса.

Рис. 3. Внешний вид Stackup Editor

Сопоставление моделей

Далее — назначим компонентам схемы соответствующие модели. Наиболее простым способом это можно сделать через меню Models -> Assign Models/Values by Reference Designators (.REF file).

В появившемся окне можно сопоставить обозначению компонента модель либо изменить параметр (для простых пассивных компонентов) (см. рис. 4.).

Для сопоставления необходимо выбрать наименование компонента в рабочей области «Design's part list», переключить круглую кнопку на .ibs в меню «Library» в правой части окна, из выпадающего списка выбрать необходимый файл модели и нажать «Assign». После чего — при благоприятном исходе сопоставления моделей — напротив наименования компонента появится зеленая галочка, символизирующая корректность сопоставление модели.

После окончания сопоставления всех моделей жмем Save для сохранения.

Рис. 4. Внешний вид окна REF-File editor

Редактирование параметров входа/выхода и тестового сигнала

В качестве примера попробуем промоделировать сигнал по цепи EMB_CLK.

Выберем цепь по названию через меню Select -> Net by Name for SI analysis. После чего подкорректируем параметры назначенной модели через Models -> Assign Models/Values by Net. Т.к. линия CLK TMS320C6745 является двунаправленной, но в нашем случае она — выход, в рабочей области Buffer settings выбираем Output (рис. 5).

Рис.5. Настройка буфера на выход

В верхних вкладках Resistor...Bead можно вбить значения для пассивных элементов. Вкладка Quick Termination позволяет настроить терминацию выводов.

Моделирование и отображение при помощи виртуального осциллографа

После того, как были выполнены все подготовитльные работы, перейдем непосредственно к моделированию.

Для этого через меню Simulate -> Run Interactive simulation (SI oscilloscope) запустим виртуальный осциллограф.

Его интерфейс интуитивно понятен. Остановимся лишь на некоторых моментах.

В рабочей области Stimulus установим круглую кнопку на пункт Per-Net/Pin и нажмем Assign… В появившемся меню для задания формы тестового сигнала нажмем Edit stimulus…

В качестве вида тестового сигнала выберем Pseudo-Random 10-го порядка. Количество повторений — 10. BitRate — 133 MHz (0.13 GBps). Для сохранения формы тестового сигнала нажмем на пиктограмму дискеты. (рис. 6) И сохраним в формате .eds.

В окне Assign Stimulus назначем сохраненный нами сигнал на цепь EMB_CLK.

Рис.6. Настройка формы тестового сигнала

Видимость отображения графиков настраивается в рабочей области «Probes:» в правом углу окна «Digital Oscilloscope».

Удаление информации с рабочей области производится по нажатии кнопки Erase.

Маркеры в нижней части окна удобны для измерения величин (по времени и напряжению) промоделированного графика.

Начало моделирования выполняется по нажатии кнопки «Start Simulation». Результаты моделирования показаны на Рис.7.

Рис.7. Результаты моделирования

Моделирование перекрестных помех включается через меню основного окна Setup -> Enable Crosstalk Simulation. Параметры моделирования перекрестных помех настраиваются в меню Setup -> Crosstalk Thresholds (возможна настрока по величине перекрестных помех и по максимальной протяженности паралелльных проводников). При включении моделирования перекрестных помех в основном окне подсвечиваются цепи-агрессоры (проходящие по пороговым значениям перекрестных помех).

Исходный файл .dsn, полученный из него .hyp и модели можно скачать здесь

7 комментариев

И очень интересует вопрос моделирования цепей питания.

Короче говоря, хочеться увидеть серию статей о HyperLynx SI/PI :-)

PCB_Designer, очень ждём Ваших статей о MG.

у megratec можно зарегистрироваться и скачать тренинги на русском. Скачал. По тексту очевидно что переводили с английского, некоторые тексты ничего, а некоторые — качество перевода никуда не годится, читать невозможно. Поискал то же на английском — нету. Спрашиваю megratec «можете ли дать ссылку на исходный документ?» -Нет не можем, нам Mentor Graphics не разрешает в электронном виде распространять тексты тренингов.

Чудаки.

C megratec скачал только тепловой анализ.

Pasha_us2iav(at)ukr.net

спасибо.