Релейная ЭВМ версия 2. Релейная логика, АЛУ.

«Доктор, я опять занимался этим всю ночь..»

В далеком 2010 году я представил общественности небольшое 4-битное АЛУ и назвал его РЦВМ-1.

О ней можно почитать ВОТ ТУТ.

Еще тогда я загорелся желанием создать вторую версию этой адской машины. Время от времени я открывал DipTrace и рисовал. Но сегодня ночью я нарисовал слишком много и представляю текущее состояние своей работы на критику и рекомендации АЛУ новой машины. Делать эту машину я буду еще несколько лет :)

Куча релейной логики под катом.

Изначальная задача звучит следующим образом:

Разработать полноценную 8-разрядную ЭВМ на базе герконовых реле.

герконовые реле были выбраны ввиду своей компактности и быстроты работы — среднее время срабатывания реле — 1мс позволяет в теории получить тактовые частоты в десятки герц.

На данный момент, при проектировании используются следующие герконовые реле:

РЭС43 — 2 управляющие катушки, 2 пары замыкающих контактов;

РЭС55 — 1 управляющая катушка, 1 пара переключающих контактов;

РЭС64А(Б) — 1 управляющая катушка, 1 пара замыкающих контактов;

РЭС83 — 2 управляющих катушки, 4 пары замыкающих контактов.

около тысячи реле в коробках. АЛУ, как оказалось, съест половину.

Поехали:

Этот вариант дает развязку левой части от правой и возможность запитать схемы от разных напряжений (так как релюхи с разными паспортами).

Одно реле это не баг, это фича — РЭС43 имеет две полноценные катушки.

А вот тут такая фича уже не прокатит — контакты на переключение.

A XOR B понадобится для совершения математической операции в АЛУ

Но если честно, то в АЛУ нужен 3-входовый XOR, дабы добавить C флаг.

Выведем A XOR B, так как она пригодится где-то дальше.

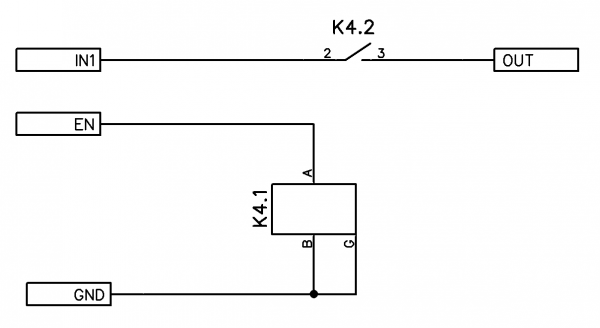

без инвертора никуда.

Однобитовый ключ.

Так как он в общем случае копирует логику И — его часто можно встретить в дальнейших схемах для экономии одного реле.

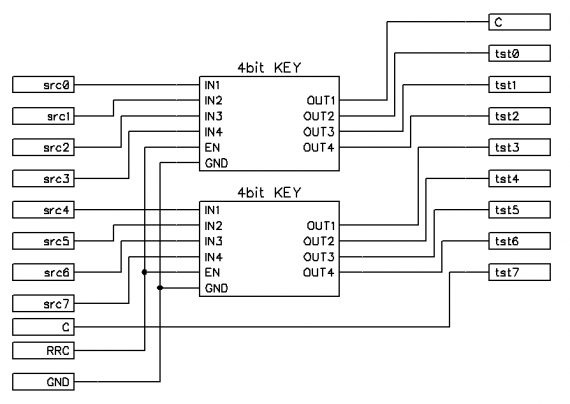

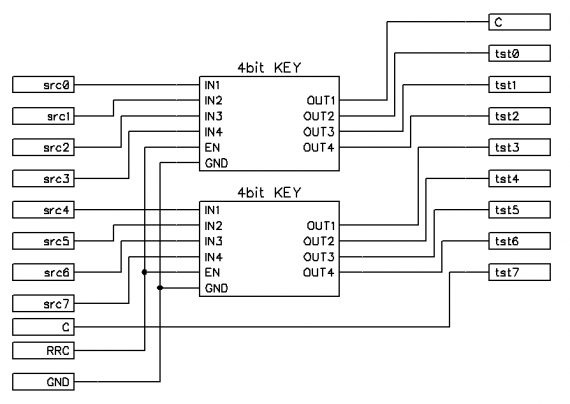

Двухбитовый ключ на сдвоенном реле.

Четырехбитовый ключ.

Ключ-инвертор. необходим для отключения блоков.

Теперь можно скомбинировать элементарную логику в более высокие уровни:

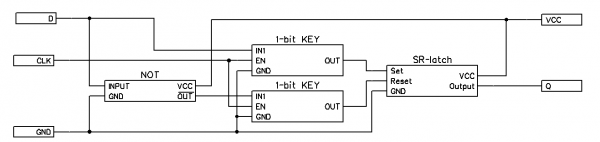

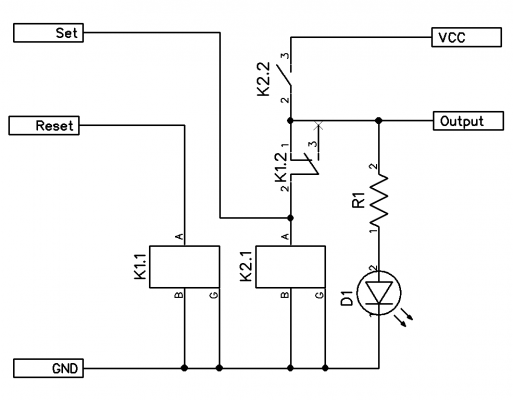

RS триггер будет основой для регистров — РОН и промежуточного

Одно реле устанавливает бит, второе сбрасывает.

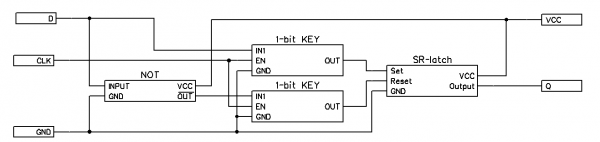

Задача этого триггера — по сигналу на синхроимпульсе сохранить данные. Для этого сигнал инвертируется (дабы правильно отрабатывать S и R сигналы) и через ключи подается на вход RS-триггера, решающего основную задачу.

Главный элемент АЛУ — сумматор с переносом. результат реализуется с помощью 3XOR,

перенос — когда как минимум два из трех входов — единины.

Так как операции сдвига работают со всеми битами и там как раз подойдут 4-битовые ключи, они сделаны отдельно:

Выходы подключаются через блок 1бит АЛУ, так как в нем реализован промежуточный буфер.

Назначение выводов:

Слева:

Актуальная схема из моего облака ЗДЕСЬ.

По блокам:

сигналы src и dst поступают на общий вход. Если выбрана команда SUB, src инвертируется. Сигналы поступают на влок мат. сложения.

Сигнал переноса выбирается в зависимости от команды. Ключ будет активирован для команд ADDC, SUB и SUBC. Для команды SUB в случае первого бита вместо внешнего сигнала переноса подается лог. 1, что дает dst+not.src+1.

По любой из команд сдвоенный ключ выведет R на TST и С на С.

Линия A XOR B через однобитовый ключ по своей команде будет подана на TST

Через блок И (вместо него использован ключ) сигнал подается на ключ результата.

Команды AND и BIT разделяются через блок ИЛИ, при этом сигнал BIT уходит на блок запрета STORE/LOAD

ИЛИ просто подается через ключ

сигнал dst умножается на инвертированный src и подается на ключ.

задача команда CMP — выдать Z при нуле, и C при переносе операции dst-src.

нуль при dst- src будет при AB=00, AB=11. как как TST проверяется на Z целиком, то просто выведем на него результат A XOR B. С будет при AB=11, выведем на него A AND B

не забудем отключить STORE/LOAD для буфера — за это отвечает двухбитовый ключ, который отключится при командах BIT и CMP.

Пока делал описание, несколько раз успел скорректировать схему. Публикую ее не для оценки целесообразности конструкции, а для конструктивной критики схемотехники.

Итого на схему 1 разряда АЛУ, без операции сдвигов 36 реле. Когда-нибудь аккуратно размещу из на одной плате и сделаю 8-разрядный модуль АЛУ на четыре сотни реле. неплохо, да :)

В далеком 2010 году я представил общественности небольшое 4-битное АЛУ и назвал его РЦВМ-1.

О ней можно почитать ВОТ ТУТ.

Еще тогда я загорелся желанием создать вторую версию этой адской машины. Время от времени я открывал DipTrace и рисовал. Но сегодня ночью я нарисовал слишком много и представляю текущее состояние своей работы на критику и рекомендации АЛУ новой машины. Делать эту машину я буду еще несколько лет :)

Куча релейной логики под катом.

Изначальная задача звучит следующим образом:

Разработать полноценную 8-разрядную ЭВМ на базе герконовых реле.

герконовые реле были выбраны ввиду своей компактности и быстроты работы — среднее время срабатывания реле — 1мс позволяет в теории получить тактовые частоты в десятки герц.

На данный момент, при проектировании используются следующие герконовые реле:

РЭС43 — 2 управляющие катушки, 2 пары замыкающих контактов;

РЭС55 — 1 управляющая катушка, 1 пара переключающих контактов;

РЭС64А(Б) — 1 управляющая катушка, 1 пара замыкающих контактов;

РЭС83 — 2 управляющих катушки, 4 пары замыкающих контактов.

около тысячи реле в коробках. АЛУ, как оказалось, съест половину.

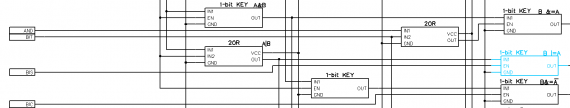

Релейная логика

Первая задача — создать основные блоки РЦВМ. Есть несколько полезных книжек по этому поводу, мне пока хватает университетского курса по релейно-контакторным схемам.Поехали:

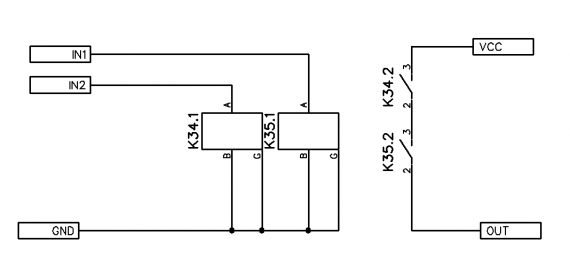

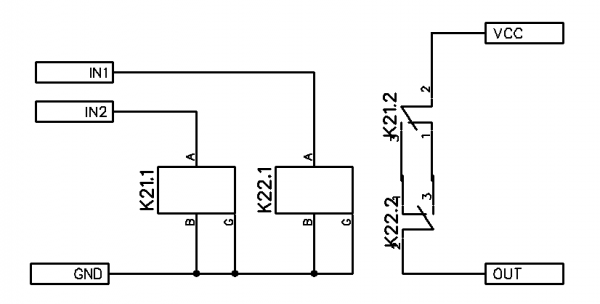

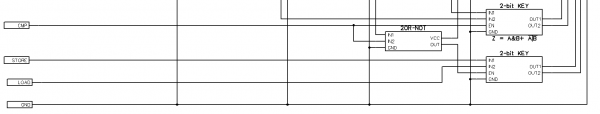

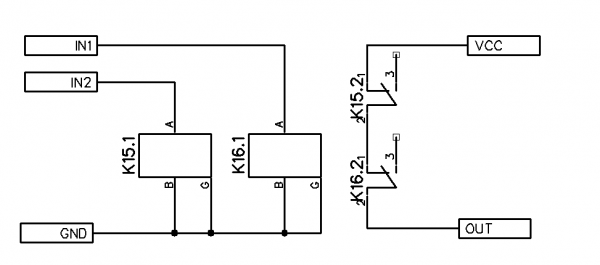

2-AND

Этот вариант дает развязку левой части от правой и возможность запитать схемы от разных напряжений (так как релюхи с разными паспортами).

2-OR

Одно реле это не баг, это фича — РЭС43 имеет две полноценные катушки.

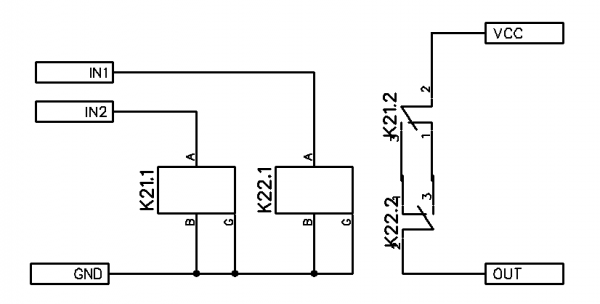

2-AND-NOT

А вот тут такая фича уже не прокатит — контакты на переключение.

2-OR-NOT

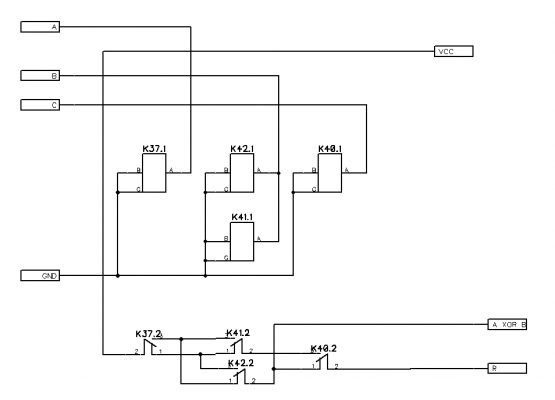

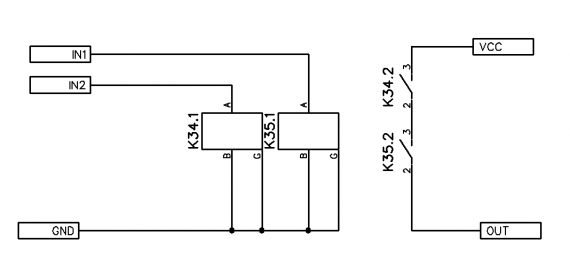

2-XOR

A XOR B понадобится для совершения математической операции в АЛУ

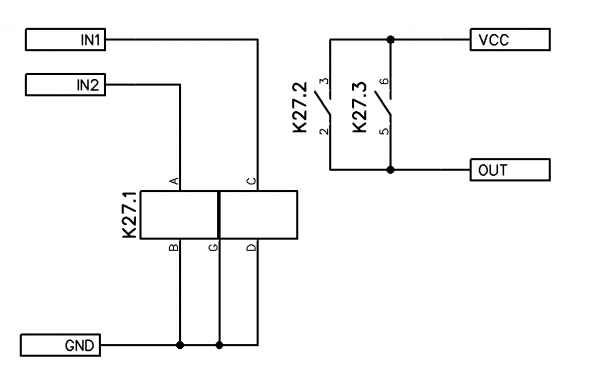

3-XOR

Но если честно, то в АЛУ нужен 3-входовый XOR, дабы добавить C флаг.

Выведем A XOR B, так как она пригодится где-то дальше.

NOT

без инвертора никуда.

Ключи

Для подключения тех или иных блоков и функций необходимы ключи:

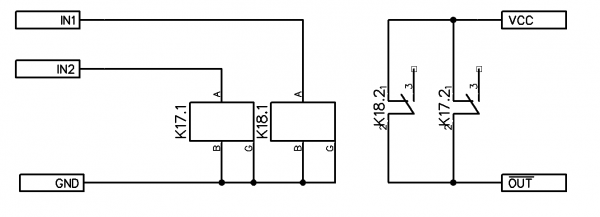

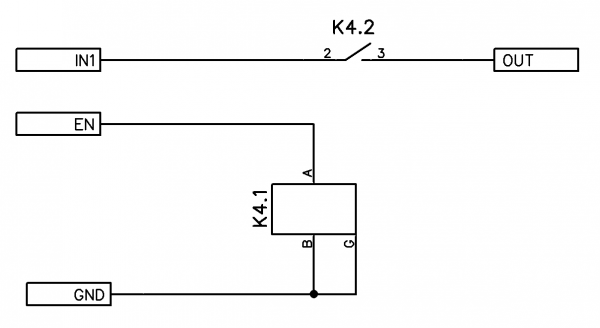

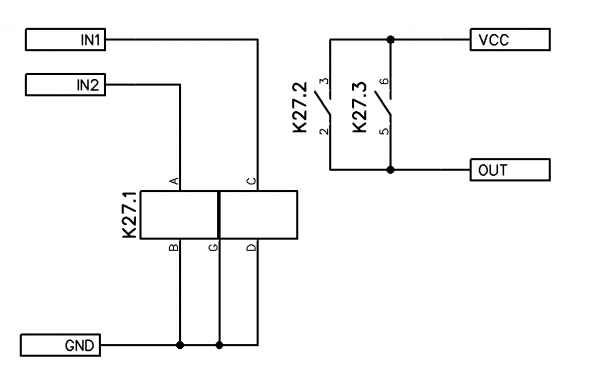

Однобитовый ключ.

Так как он в общем случае копирует логику И — его часто можно встретить в дальнейших схемах для экономии одного реле.

Двухбитовый ключ на сдвоенном реле.

Четырехбитовый ключ.

Ключ-инвертор. необходим для отключения блоков.

Переключатель

Для выбора одного режима из двух необходим простой переключатель:

Теперь можно скомбинировать элементарную логику в более высокие уровни:

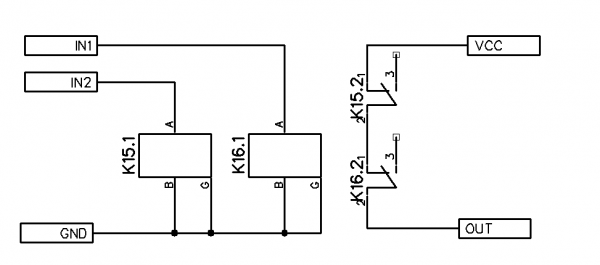

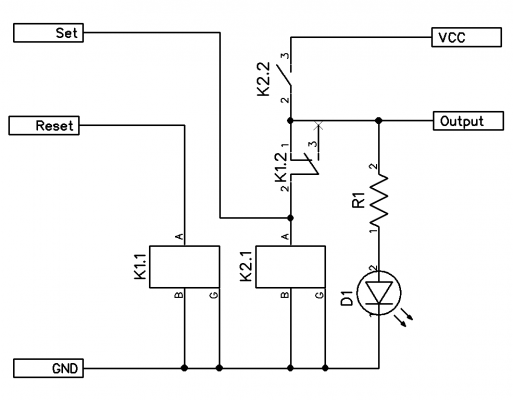

SR-триггер

RS триггер будет основой для регистров — РОН и промежуточного

Одно реле устанавливает бит, второе сбрасывает.

синхронный D-триггер

Задача этого триггера — по сигналу на синхроимпульсе сохранить данные. Для этого сигнал инвертируется (дабы правильно отрабатывать S и R сигналы) и через ключи подается на вход RS-триггера, решающего основную задачу.

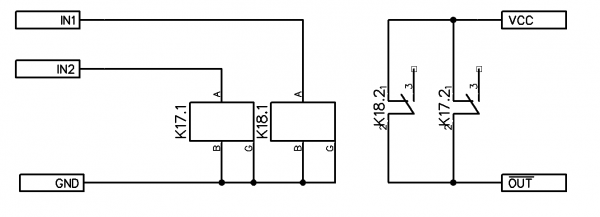

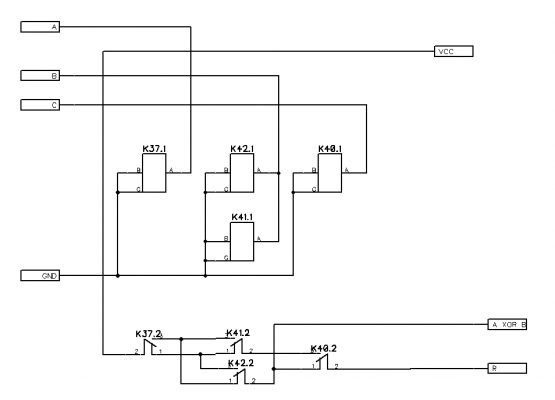

1 bit ADD+C

Главный элемент АЛУ — сумматор с переносом. результат реализуется с помощью 3XOR,

перенос — когда как минимум два из трех входов — единины.

Система команд

Так как мне безумно нравится MSP430, я решил частично скопировать его систему команд по работе с арифметикой и логикой. Причем будем придерживаться логике нативых и эмулируемых команд — про последние не забудем на этапе создания компилятора:- ADD — dst = dst+src, не забудем отключить вход C;

- ADDC — dst = dst+src+C;

- SUB — dst = not.src + dst + 1, не забудем подать 1 вместо C на вход С нулевого бита

- SUBC — dst = dst+scr+C;

- XOR — dst = dst XOR src;

- AND — dst &=src;

- BIT — dst&src, управляет флагами, но не копирует результат. не забыть отключить сигнал STORE

- BIC — dst &= ~src — инвертируем вход и делаем лог. умножение;

- BIS — dst |=src;

- RRA — MSB -> MSB… LSB ->C, арифметический сдвиг вправо;

- RRC — C-> MSB… LSB ->C, циклический сдвиг вправо, не забыть, что читается старое значение С, а пишется новое

- CMP — TST = A XOR B, C = A*B, описание ниже

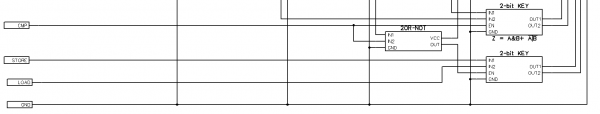

АЛУ

Так как предполагаемый объем реле на 1 бит будет существенным, принято решение создать 1 битовую имплементацию АЛУ, которую блоками расположить на общей печатной плате. В теории, при Внезапном наличии нескольких тысяч реле железку можно будет расширить по 16 бит :)Так как операции сдвига работают со всеми битами и там как раз подойдут 4-битовые ключи, они сделаны отдельно:

RRA

RRC

Выходы подключаются через блок 1бит АЛУ, так как в нем реализован промежуточный буфер.

блок 1 бит АЛУ

Назначение выводов:

Слева:

- C — перенос с предыдущего разряда или из регистра;

- 0bit=1 — устанавливается для 0 разряда для операции SUB;

- src — разряд регистра источника;

- dst — разряд регистра приемника;

- ADD — на TST результат сложения;

- ADDC — на TST результат сложения с переносом;

- SUB — на TST результат отрицания;

- SUBC — на TST результат отрицания с переносом;

- AND — на TST результат логического умножения;

- BIT — на TST результат логического умножения без записи в промежуточный регистр;

- BIS — на TST результат логического сложения;

- BIC — на TST результат сброса бита;

- XOR — на TST результат математического сложения;

- CMP — на TST результат проверки на Z без записи в регистр. Также проверяется C;

- STORE — попытка записи TST в буфер;

- LOAD — попытка выгрузки данных из буфера;

- VCC — питание. предположительно 12В;

- rslt — прочтенные данные из буфера;

- TST — результат операции. По нему производятся оценка N(bit7=1),Z(bit0...bit7=0);

- С — флаг переноса. По нему определяются полуперенос-H(bit4=1), и переполнение (V=C8)

Актуальная схема из моего облака ЗДЕСЬ.

По блокам:

ADD/SUB

сигналы src и dst поступают на общий вход. Если выбрана команда SUB, src инвертируется. Сигналы поступают на влок мат. сложения.

Сигнал переноса выбирается в зависимости от команды. Ключ будет активирован для команд ADDC, SUB и SUBC. Для команды SUB в случае первого бита вместо внешнего сигнала переноса подается лог. 1, что дает dst+not.src+1.

По любой из команд сдвоенный ключ выведет R на TST и С на С.

Линия A XOR B через однобитовый ключ по своей команде будет подана на TST

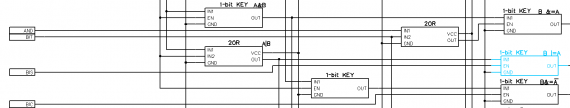

AND BIT BIS

Через блок И (вместо него использован ключ) сигнал подается на ключ результата.

Команды AND и BIT разделяются через блок ИЛИ, при этом сигнал BIT уходит на блок запрета STORE/LOAD

ИЛИ просто подается через ключ

BIC

сигнал dst умножается на инвертированный src и подается на ключ.

CMP

задача команда CMP — выдать Z при нуле, и C при переносе операции dst-src.

нуль при dst- src будет при AB=00, AB=11. как как TST проверяется на Z целиком, то просто выведем на него результат A XOR B. С будет при AB=11, выведем на него A AND B

не забудем отключить STORE/LOAD для буфера — за это отвечает двухбитовый ключ, который отключится при командах BIT и CMP.

Пока делал описание, несколько раз успел скорректировать схему. Публикую ее не для оценки целесообразности конструкции, а для конструктивной критики схемотехники.

Итого на схему 1 разряда АЛУ, без операции сдвигов 36 реле. Когда-нибудь аккуратно размещу из на одной плате и сделаю 8-разрядный модуль АЛУ на четыре сотни реле. неплохо, да :)

12 комментариев

Когда подается импульс на Set, через K2.1 начинает течь ток. Оно замыкает контакты K2.2 и начинает питать само себя. Таким образом, битик записался. Чтоб сбросить битик, нужно подать импульс на reset — K1.2 разомкнется и K2.1 отключится.

проснулся утром и перерисовал сумматор, уменьшив число реле с 10 до 7 (уверен это не предел) и D-триггер — с 5 до 4 :) Когда только одних триггеров во всем компьютере полторы сотни(17*8), важна каждая капля :)

Вместо инвертора и двух блоков И один ключ и один переключатель.

Сигналом на D выбираем сброс или установку, а сигналом клок подаем ииницу на вход переключателя.

Но это задача следующих выходных :)

Правую часть совсем не понял — то что подписано LATCH это типа катушка третьего реле?

А за счет чего оно удерживается при отсутствии D и C(ведь питание идет через них) и как переключается?

И как сигнал C влияет на запись?

но если предположить, что я не увидел тонкой авторской предпосылки, то я вижу два переключающих контакта — а это опять два реле — один герконник с двумя переключающими контактами я не встречал, а два герконника — это уже 4 реле.

Сейчас глянул на схему регистра машины Гарри Портера — он перед записью просто обрубает всем триггерам регистра питание, они сбрасываются и он заливает новые данные :) Надо подумать над этим вариантом — минус 7*17 реле ) Но это будет синхронный буффер…

С низу — симметрично. Смысл в том, что когда клок нулевой, релюха-защелка находится в устойчивом состоянии. Когда клок высокий, ветка по которой она питается зависит от данных.

Естественно, есть «нюанс» в том, что при падающем клоке релюха может выключится до того, как включится основное питание, но это должен решить небольшой конденсаторчик :)

Но раз не бывает таких реле, то и уменьшить врядли получится.

Так что триггеры сделаю по последней своей, а в регистры как у Гарри Портера сделаю с общим сбросом — там вовсе 2 реле на бит + 1 останется = 17 реле на буфер. и переключатель не нужен.

Причем небольшая область памяти будет выводиться на светодиодную матрицу 32х16 — надо же ее уже куда-нибудь пристроить, а то лежит без дела.

Я не ставлю перед собой задачу сделать простую машину. Можно и аппаратный брейнфак замутить, но смысл?:)